基于ARM核與DSP核組成的OMAP5910嵌入式系統

開放式多媒體應用平臺(Open Multimedia Application Platform,OMAP)處理器系列包括應用處理器及集成的基帶應用處理器,具有高性能、實時處理及超低功耗的特點,廣泛應用于PDA、Web記事本、遠程通信和醫療器械等。

本文引用地址:http://www.104case.com/article/257614.htmOMAP5910處理器是由TI公司的應用最為廣泛的TMS320C55x DSP內核與低功耗、增強型ARM925微處理器組成的雙核應用處理器,是OMAP系列的最新成員。TMS320C55x系列可提供對低功耗應用的實時多媒體處理的支持,而ARM925 MPU 可滿足控制和接口方面的處理需要。OMAP5910處理器同時擁有二種產品的最佳性能,包括TI TMS320C55x DSP內核的實時處理性能與低功耗、TI增強型ARM925微處理器的靈活性,且通過優化處理器間的通信機制,使設計者可同時享受這二種處理器的最大優點。基于雙核結構,OMAP5910具有極強的運算能力和極低的功耗,一方面產品性能高、省電,另一方面同其他OMAP處理器一樣,采用開放式、易于開發的軟件設施,支持廣泛的操作系統,如Linux、Windows、WinCE、Nucleus、Palm OS、VxWorks、Java等。此外,還可以通過API及用戶熟悉且易于使用的工具優化其應用程序。

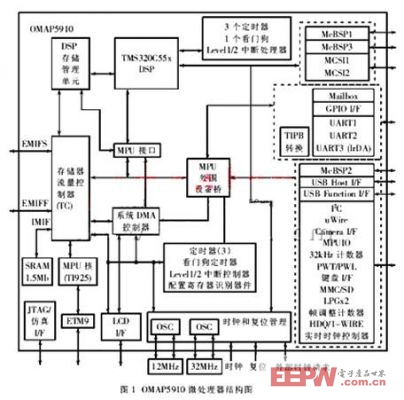

1 OMAP5910的結構及特點

OMAP的結構圖如圖1所示。

1.1 OMAP5910處理器的主要特點

(1)高性能。采用低功耗、高性能的32位ARM9TDMI內核和TMS320-C55x DSP內核,工作頻率高達150MHz;采用5級的整數流水線結構;支持多媒體處理技術,采用的是TMS320C55x DSP內核,增強了對視頻和音頻的解碼能力。

(2)低功耗。多電源管理模式,雙內核電壓供給為1.6V;ARM9TDMI內核具有16KB指令和8KB數據Cache,TMS320C55x DSP內核具有24KB的指令Cache;支持2.75V的存儲器和3.3V的I/O接口。

(3)I/O擴展。有4個16位的FLASH/SRAM的存儲空間,1個16位的SDRAM存儲空間。

(4)外圍控制接口。9通道系統可配置DMA控制器;LCD控制器,支持專用的LCD DMA方式,并支持STN(passive monochrome,俗稱單彩)、TFT(active color,俗稱真彩)、STN(passive color,俗稱偽彩)顯示;串行端口(3個UARTs、IrDA、I2C、3個McBSPs、2個MCSIs、MicrowireTM、PWT、PWL、uWire、HDQ/1-Wire);USB接口;支持MMC/SD卡。

(5)時鐘控制。時鐘源:32.768kHz的振蕩器;12MHz/13MHz的振蕩器;可編程的內核鎖相環。

(6)電源管理。Awake模式(正常運行模式)、Big-sleep模式(省電模式)、Deep-sleep(省電模式)模式。

(7)封裝形式。289腳GZG BGA封裝或GDY BGA封裝。1.2 TI925T(ARM9TDMI)內核

TI925T(ARM9TDMI)內核是采用5階段管道化流水線32位的RISC處理器架構的體系結構,并采用ARM9作內核,同時配備Thumb擴展。它能夠處理32位或者16位的指令和8位、16位、32位的數據。這款新型高性能、低功耗的微構架兼容ARMv4T指令集,并通過采用協處理器CP15使體系結構得到增強。系統中的控制寄存器可通過對協處理器CP15的讀寫來對MMU、Cache和讀寫緩存控制器進行存取操作。這種微構架在ARM核的周圍提供了:指令與數據存儲器管理單元,指令、數據和寫緩沖器,性能監控、調試和JTAG單元以及協處理器接口,MAC協處理器和內核存儲總線。

TI925T 的MMU具有2個64個項的轉換旁路緩存器(TLB)用于指令和數據流,每項均可映射存儲器的段、大頁和小頁。為了保證內核周期的存取指令和數據,TI925T包含了分別獨立的1個16KB的指令Cache和8KB的數據Cache。二者獨立的好處是可以在同一時鐘周期內讀取指令和數據,而不需要雙端口的Cache。指令和數據Cache都是2路相互關聯的Cache,以16B為1塊進行操作,并采用最小最近使用(LRU)算法以刷新存儲。另外,TI925T還提供了寫緩沖的性能用于提升內核,其能夠緩沖數據的容量高達17字。

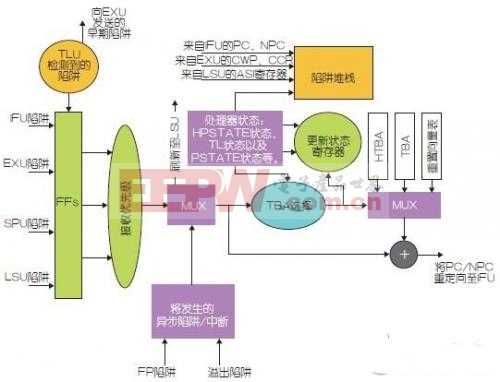

1.3 TMS320C55x內核

TMS320C55x內核的主要特點是:有1個64×8位的緩存隊列(Instruction Buffer Queue),2個17位×17位的乘法累加單元(MAC),1個40位的算術邏輯單元(ALU),1個16位的算術邏輯單元,1個40位的桶形移位器(Barrel Shifter)和4個40位的加法器。另外還有12條獨立的總線,即:3條數據讀總線,2條數據寫總線,5條數據地址總線,1條程序讀取總線和1條程序地址總線。此外,還有用戶可以配置的IDLE域。內核主要由4個單元組成:指令緩沖單元(I單元)、程序流單元(P單元)、地址數據流單元(A單元)和數據運算單元(D單元)。

1.4 系統控制功能

OMAP5910微處理器的系統控制模塊提供了實時時鐘(RTC)、看門狗(WT)、中斷控制器、功率管理控制器、復位控制器和2個片上振蕩器。

1.5 時鐘和電源管理

OMAP5910微處理器提供了2個振蕩器以輔助管理電源耗損。設計系統時,在待機模式下可以直接關閉12MHz的振蕩輸入,只留下32kHz振蕩器來維持系統運作。這樣,不但可以保證系統運行,讓需要維持運行的周邊正常操作(例如用戶可以通過Keypad等輸入裝置來喚醒整個系統),而且可以很容易地關閉大部分接口設備,達到控制電源耗損的目的。

電源管理有3種工作模式:Awake模式、Big sleep模式和Deep sleep模式。Awake模式下,整個芯片運行在峰值頻率,32kHz振蕩器和12MHz振蕩器正常工作。當時鐘請求時,可使能外圍器件的12MHz時鐘,并由ULPD DPLL或APLL產生48MHz時鐘。當芯片產生IDLE請求時,芯片工作:在Big sleep模式下,DPLLs 1、內部12MHz時鐘被關閉。在Deep sleep模式下,只有32kHz振蕩器正常工作,整個系統工作將處于最低功耗狀態。

1.6 EMIFS、EMIFF接口和存儲器

在OMAP5910微處理器核心中,提供了2個擴充內存接口:EMIFS和EMIFF。EMIFS接口可以支持128MB的異步靜態存儲器(ASRAM)、FLASH和ROM。EMIFF接口可以設定為用來操作同步動態存儲器(SDRAM),其尋址空間高達128MB。這2個內存接口都是獨立運作,可以同時經由微處理器核心存取數據,也可以利用直接內存存取(DMA)數據。另外還有一個內部存儲器區(IMIF接口的SRAM),用來連接OMAP5910微處理器內部的內存,實現常用的數據存取,如用作微處理器液晶屏幕顯示的圖像緩沖器。而內存間數據傳輸的控制則由Traffic Controller(流量控制器)來控制,Traffic Controller會對各種傳輸需求依設定的優先級來執行數據的傳送。

1.7 外圍控制模塊

OMAP5910微處理器有9個獨立通道和7個接收/發送端口的DMA控制器。DMA控制器可響應內部和外部設備的請求,在MPU TI925T(ARM9TDMI)運行條件下,完成外部寄存器、內部寄存器和外部設備之間的數據傳輸。系統DMA的設置取決于MPU TI925T(ARM9TDMI)內核。

此外,OMAP5910微處理器還有一個獨立的DMA通道供LCD控制器專用。LCD控制器提供了支持被動彩色方式STN(偽彩)和主動彩色方式TFT(真彩)顯屏接口,并支持被動單色STN格式。OMAP5910擁有自己專用的通道DMA控制器來控制面板的顯示,所支持的最大顯示分辨率為1024×1024象素,在單色模式下,能支持15級灰度。在STN顯示模式下,彩色顯示最高支持3 375種顏色;而在TFT顯示模式下,彩色顯示最高支持65 536種顏色。LCD控制器將幀緩存中的象素編碼值對應12位寬的256個入口的調色板RAM,并根據數據寬度決定彩色的數量。通常可選用片內共享的SRAM或者通過EMIFF接口選用外部SDRAM來當作幀緩存器(為優化性能推薦選用片內共享的SRAM)。

OMAP5910微處理器支持的串口包括:基于通用串行總線2.0版本和開放式主機控制接口1.0a版本的USB Function and Host模塊接口;3個通用異步收發口(UARTs),其中2個UARTs具有自動調節波特率的性能,其波特率調節范圍在1 200bps~115.2kbps之間,而另外1個URAT通常用作一般的URAT或者用作IrDA接口使用;3個多通道緩沖串行口(McBSPs)可提供高達128個通道的高速、全雙工通信的串行接口,可直接與T1/E1調幀器相連接,并支持兼容MVIP、ST-BUS、IOM2、AC97、I2S等協議的設備;2個多通道串行口(MCSI)提供了全雙工通信以及對主/從時鐘的控制功能,同時為TMS320C55x 內核對外部設備如:多媒體數字音頻解碼編碼器或其他模擬轉換器等的訪問提供便利的通信接口;基于Philips I2C-BUS 2.1版本的I2C Master/Slave接口(支持多主機(Multimaster)模式),即在I2C總線上的設備(包括OMAP5910在內)都可充當接收機或發送機;支持MMC/SD或SPI協議并傳輸串行數據的MMC/SD卡接口和1個SPI接口。

評論