基于DSP與串行A/D組成的高速并行數據采集系統方案

系統硬件設計

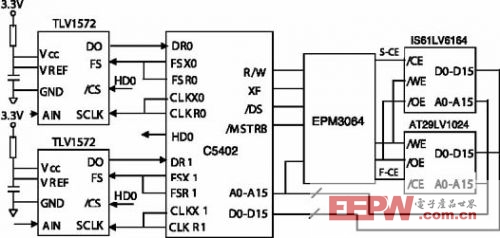

在分析了C5402多通道緩沖串口和串行A/D轉換器TLV1572工作特點后,可以利用TLV1572工作在DSP模式,使其與C5402進行接口,在同步時鐘信號的作用下完成A/D轉換的數據傳輸。圖3為整個數據采集系統的硬件原理圖,本系統根據C5402的多通道緩沖串口特性,充分利用兩個緩沖串口與兩片串行A/D TLV1572進行數據傳輸。

為了達到與C5402很好匹配,A/D電源和參考電壓都接了3.3V。A/D的FS接DSP的FSX和FSR,使數據輸入的幀同步信號由DSP產生。SCLK接DSP的CLKX和CLKR,這樣數據的輸入和輸出時鐘均來自DSP。C5402與兩片A/D進行數據傳輸時,設置串口中斷工作在00模式,即串口數據到達觸發中斷,這樣CPU可以根據哪片A/D傳輸數據產生相應的串口中斷RINT0或RINT1。當兩個串口的數據同時到達,即同時申請中斷時,C5402的CPU會根據中斷優先級響應RINT0中斷,然后再響應中斷RINT1。為了保證數據通信的可靠性,避免數據沖突,在響應RINT1中斷的過程中,串口0無中斷請求。

C5402芯片內配置有4K×16bit片內屏蔽式的ROM(F000-FFFF)。在4K ROM資源里包含了Bootloader程序,它允許程序放在外部較慢的存儲器或微處理器中,并調到高速的DRAM存儲器中運行,大大減小了C5402內部掩膜的需要,降低了電路設計成本。系統獨立工作的內部邏輯由CPLD來完成,如圖4所示。

C5402上電復位裝載時,由于Bootloader程序在初始化時設置XF為高電平,在系統進入并行引導裝載模式后,C5402從數據尋址為0FFFFh單元(A15=1,選中Flash)中讀取將要載入的程序存儲區首地址,和并行轉載數據流。此時,C5402可以將AT29LV1024 Flash地址08000h~0FFFFh單元中的數據讀到C5402對應于0000h~7FFFh尋址區的片內DARAM和片外SRAM IS61LV6164中。

Bootloader程序結束后,在這個系統中,用戶程序的第一條語句為RSBX XF,即置XF引腳為低電平,Flash始終不選通。這樣,SRAM的高32K區域(08000h~0FFFFh)被釋放出來,可以作為DSP系統運行時的數據區或程序區使用。

系統軟件設計

系統的軟件設計主要包括多通道緩沖串口的初始化、串口中斷服務程序和并行裝載程序設計等。

● 程序設計應注意的問題

(1)McBSP工作在數據接收中斷方式,因此全局中斷和串口中斷的相應位應該合理設置。同時,在設置中斷向量表時,使中斷向量表的位置與處理器模式狀態寄存器PMST中的中斷向量指針IPTR相對應,使IPTR的9位地址指向128字的中斷向量所在的程序頁,同時,中斷向量表要嚴格按照C5402規定的格式編寫,否則不能正確地產生需要的中斷結果。

(2)要實現DSP數據采集系統的脫機獨立運行,需要給每臺DSP配備獨立的程序存儲器,在整個系統上電或者復位時,由引導裝載程序將存于片外的程序代碼裝載到片內DARAM或者系統的擴展存儲器中,然后運行程序來完成對McBSP進行設置和其他程序。

(3)為了實現兩路A/D和C5402之間的時序匹配,避免數據沖突,需要注意C5402采樣率發生寄存器SRGR1中CLKGDV位的設置,使C5402工作時鐘周期大于兩個串口中斷的響應時間。

若TLV1572以400KSPS轉換速率來計算,每片A/D應該是每2.5μs向DSP發送一次數據,申請中斷,CPU響應中斷來接收數據。DSP工作在100MHz時,時鐘周期為10ns,因此每個緩沖串口中斷服務程序中可以執行一個少于125個時鐘周期的程序而不影響串口的接收,若串口中斷程序的時間不夠用,還可以適當降低A/D轉換速率,為串口中斷提供更長的中斷服務時間。

● 串口接收的部分初始化程序

下面根據多通道緩沖串口的特性和兩路串行A/D工作的要求,主要介紹一下串口接收的軟件設計和串口部分關鍵設置。

;=====初始化串口0=====

stm #0, SPSA0

stm #0000h, SPSD0 ; #0000H寫入SPCR10

stm #1, SPSA0

stm #0000h, SPSD0 ; #0000H寫入SPCR20

stm #2, SPSA0

stm #0040h, SPSD0 ; #0040H寫入RCRC10,每字16位

stm #3, SPSA0

stm #0040h, SPSD0 ; #0040H寫入RCR20,每幀一段,每段一字

stm #6, SPSA0

stm #000fh, SPSD0 ; #0009H寫入SRGR10,時鐘周期CLKG=6.4MHz

stm #7, SPSA0

stm #300fh, SPSD0 ; #3010H寫入SRGR20,幀周期為16個CLKG

stm #0eh,SPSA0

stm #0a04h, SPSD0 ; #0A04H寫入PCR0,FSX, CLKX輸出,FSR,CLKR輸入

;=====初始化串口1=====

串口1的初始化程序參見串口0

;=====啟動接收=======

stm #0,SPSA0

stm #0001h, SPSD0 ;啟動串口0接收

stm #1,SPSA0

stm #00c0h, SPSD0 ;內部產生時鐘產生FSG

stm #0,SPSA1

stm #0001h, SPSD1 ;啟動串口1接收

stm #1,SPSA1

stm #00c0h, SPSD1 ;內部產生時鐘產生FSG

;==串口0接收中斷子程序===

.sect brint0

host_brint0:

rsbx intm ;關中斷

ldm drr0,A

stl A,*ar4+ ; 接收

……

其他處理程序

rete

結束語

本文介紹了兩片串行A/D與C5402組成的數據采集系統,該系統硬件連接簡單,A/D的采樣率可以通過串口時鐘靈活設置,通用性強。該數據采集系統已經成功應用到實驗室的信號處理系統中,顯示出設計靈活、高速、可靠等優點。

評論