嵌入式系統基礎之:嵌入式軟件開發流程

(2)硬件調試。

相對于軟件調試而言,使用硬件調試器可以獲得更強大的調試功能和更優秀的調試性能。硬件調試器的基本原理是通過仿真硬件的執行過程,讓開發者在調試時可以隨時了解到系統的當前執行情況。目前嵌入式系統開發中最常用到的硬件調試器是ROMMonitor、ROMEmulator、In-CircuitEmulator和In-CircuitDebugger。

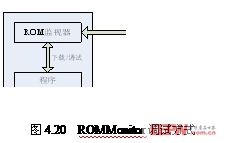

n 采用ROMMonitor方式進行交叉調試需要在宿主機上運行調試器,在宿主機上運行ROM監視器(ROMMonitor)和被調試程序,宿主機通過調試器與目標機上的ROM監視器遵循遠程調試協議建立通信連接。ROM監視器可以是一段運行在目標機ROM上的可執行程序,也可以是一個專門的硬件調試設備,它負責監控目標機上被調試程序的運行情況,能夠與宿主機端的調試器一同完成對應用程序的調試。

在使用這種調試方式時,被調試程序首先通過ROM監視器下載到目標機,然后在ROM監視器的監控下完成調試。

優點:ROM監視器功能強大,能夠完成設置斷點、單步執行、查看寄存器、修改內存空間等各項調試功能。

確定:同軟件調試一樣,使用ROM監視器目標機和宿主機必須建立通信連接。

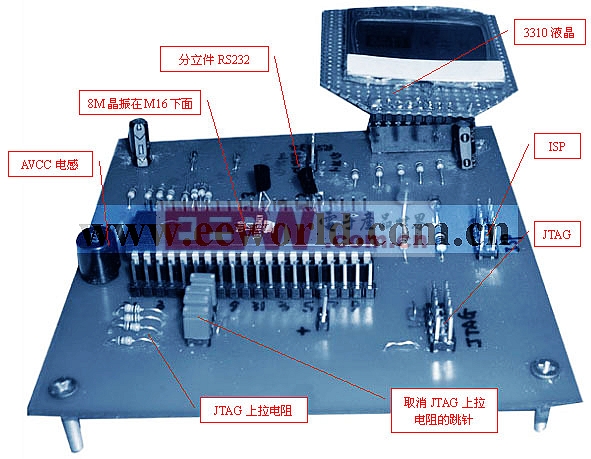

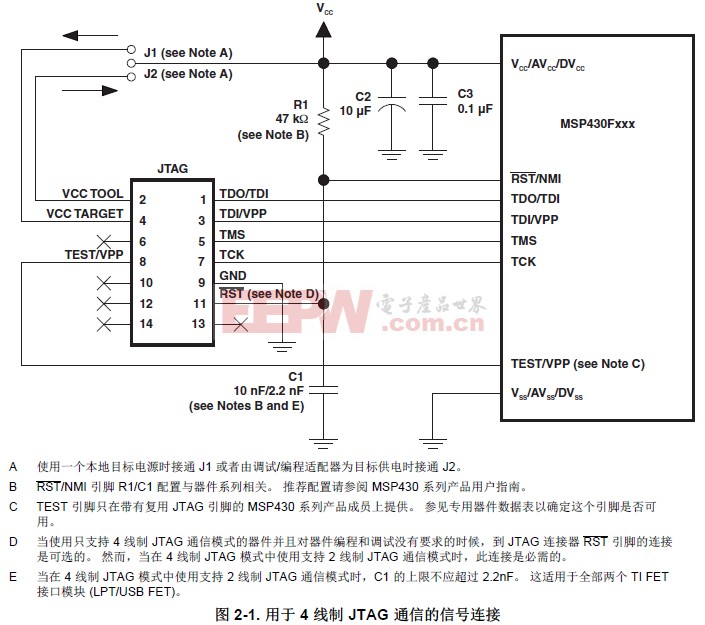

其原理圖如圖4.20所示。

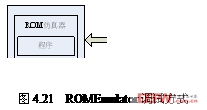

n 采用ROMEmulator方式進行交叉調試時需要使用ROM仿真器,并且它通常被插入到目標機上的ROM插槽中,專門用于仿真目標機上的ROM芯片。

在使用這種調試方式時,被調試程序首先下載到ROM仿真器中,因此等效于下載到目標機的ROM芯片上,然后在ROM仿真器中完成對目標程序的調試。

優點:避免了每次修改程序后都必須重新燒寫到目標機的ROM中。

缺點:ROM仿真器本身比較昂貴,功能相對來講又比較單一,只適應于某些特定場合。

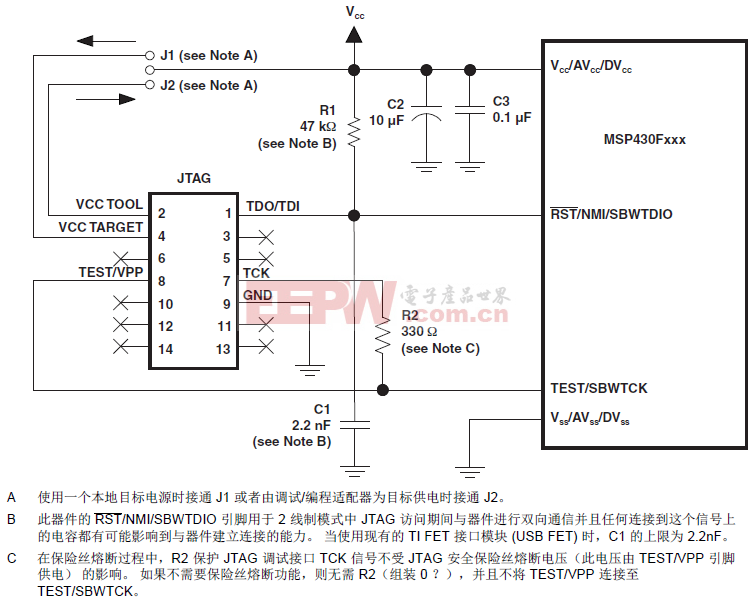

其原理如圖4.21所示。

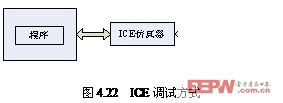

n 采用In-CircuitEmulator(ICE)方式進行交叉調試時需要使用在線仿真器,它是目前最為有效的嵌入式系統的調試手段。它是仿照目標機上的CPU而專門設計的硬件,可以完全仿真處理器芯片的行為。仿真器與目標板可以通過仿真頭連接,與宿主機可以通過串口、并口、網線或USB口等連接方式。由于仿真器自成體系,所以調試時既可以連接目標板,也可以不連接目標板。

在線仿真器提供了非常豐富的調試功能。在使用在線仿真器進行調試的過程中,可以按順序單步執行,也可以倒退執行,還可以實時查看所有需要的數據,從而給調試過程帶來了很多的便利。嵌入式系統應用的一個顯著特點是與現實世界中的硬件直接相關,并存在各種異變和事先未知的變化,從而給微處理器的指令執行帶來各種不確定因素,這種不確定性在目前情況下只有通過在線仿真器才有可能發現。

優點:功能強大,軟硬件都可做到完全實時在線調試。

缺點:價格昂貴。

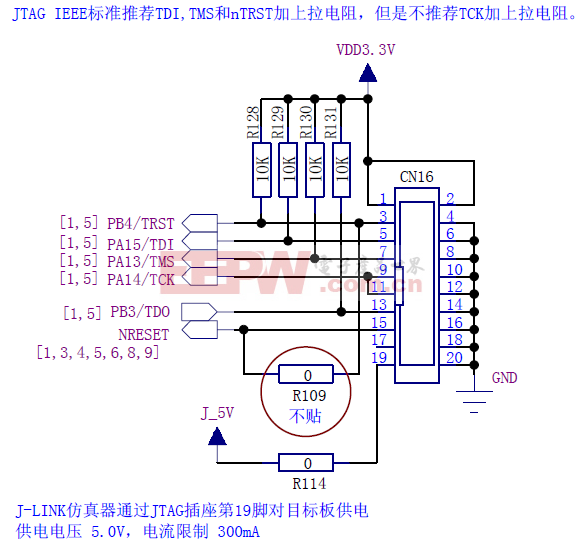

其原理如圖4.22所示。

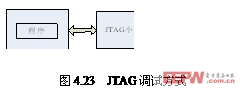

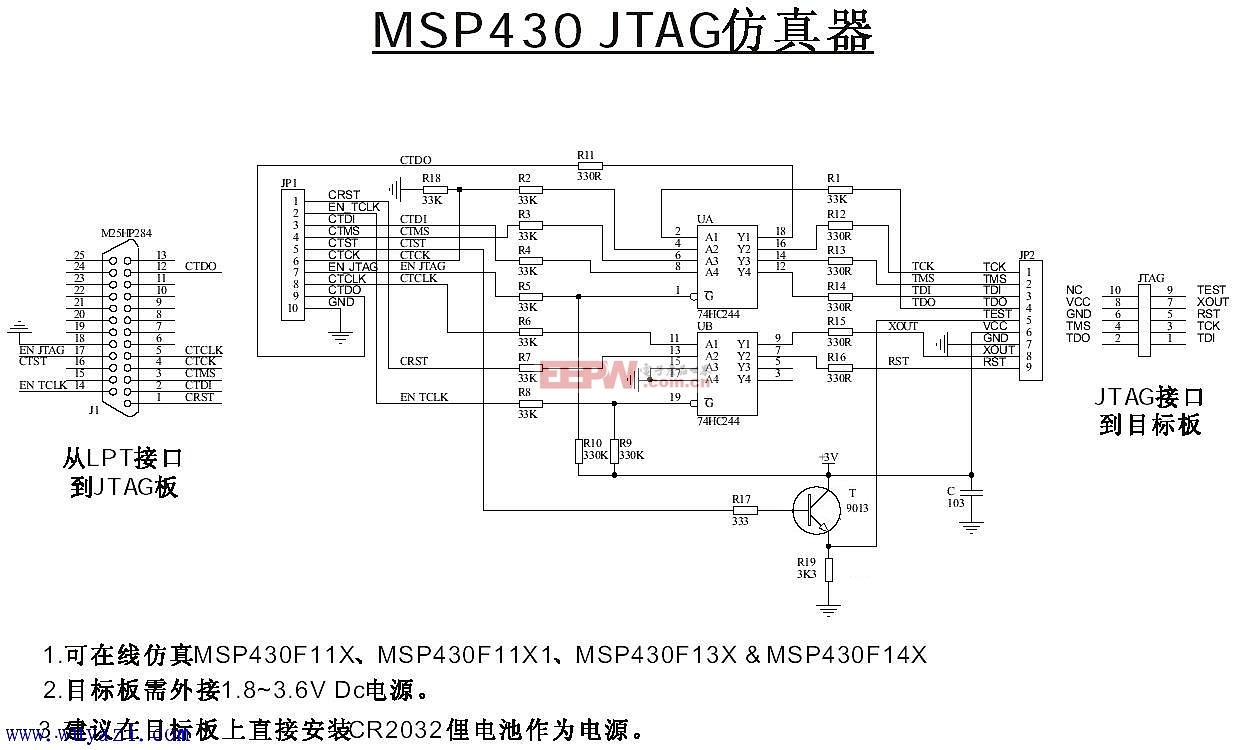

n 采用In-CircuitDebugger(ICD)方式進

行交叉調試時需要使用在線調試器。由于ICE的價格非常昂貴,并且每種CPU都需要一種與之對應的ICE,使得開發成本非常高。一個比較好的解決辦法是讓CPU直接在其內部實現調試功能,并通過在開發板上引出的調試端口發送調試命令和接收調試信息,完成調試過程。如使用非常廣泛的ARM處理器的JTAG端口技術就是由此而誕生的。

JTAG是1985年指定的檢測PCB和IC芯片的一個標準。1990年被修改成為IEEE的一個標準,即IEEE1149.1。JTAG標準所采用的主要技術為邊界掃描技術,它的基本思想就是在靠近芯片的輸入輸出管腳上增加一個移位寄存器單元。因為這些移位寄存器單元都分布在芯片的邊界上(周圍),所以被稱為邊界掃描寄存器(Boundary-ScanRegisterCell)。

當芯片處于調試狀態時候,這些邊界掃描寄存器可以將芯片和外圍的輸入輸出隔離開來。通過這些邊界掃描寄存器單元,可以實現對芯片輸入輸出信號的觀察和控制。對于芯片的輸入管腳,可通過與之相連的邊界掃描寄存器單元把信號(數據)加載到該管腳中去;對于芯片的輸出管腳,可以通過與之相連的邊界掃描寄存器單元“捕獲”(CAPTURE)該管腳的輸出信號。這樣,邊界掃描寄存器提供了一個便捷的方式用于觀測和控制所需要調試的芯片。

現在較為高檔的微處理器都帶有JTAG接口,包括ARM7、ARM9、StrongARM、DSP等,通過JTAG接口可以方便地對目標系統進行測試,同時,還可以實現Flash編程,這是非常受歡迎的。

優點:連接簡單,成本低。

缺點:特性受制于芯片廠商。

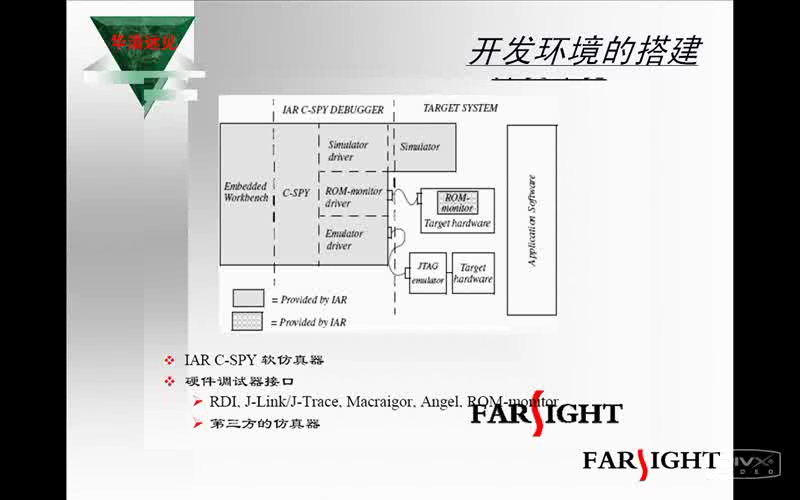

其原理如圖4.23所示。

評論