模擬與數字的智能集成解決棘手的嵌入式系統問題

高速逐次逼近型寄存器(SAR) ADC非常適合這種應用,因為,此類ADC擁有適當的精度(13 ENOB),其超快的轉換速率可支持較高頻率的控制環路,能對多個輸入通道進行多路復用,還具有低延遲( 1μS)的特性。該系統有兩個ADC,用于對電網電流和電壓進行同步采樣。需要大量輸入通道來連接ADC,以便對系統中的多個點進行監控——有時最多需要24個通道。為滿足該要求,我們設計了帶緩沖功能的特殊多路復用通道,并與ADC接口。

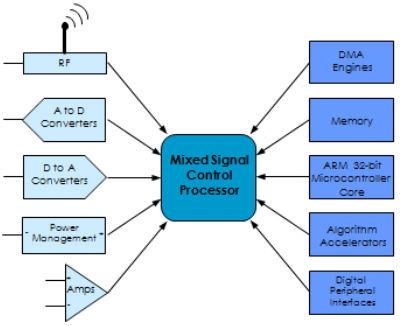

為了支持多級轉換和高速控制環路,需要選擇架構性能適當且具備高速運行能力的處理器內核。在本例中,設計溫度范圍運行速率大于200 MHz的ARM Cortex-M4即可滿足該需求。

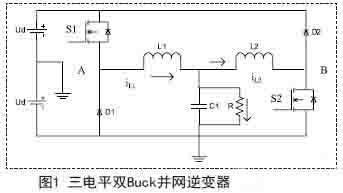

正弦濾波器(如圖2所示)與隔離式ADC結合使用。這樣可對電網中的電流以及直流注入進行測量,以防止變壓器飽和。傳統方法是用一個霍爾效應電流傳感器,但與隔離式ADC相比,這種方法成本較高。該方法假定,正弦濾波器集成于混合信號控制處理器之中,從而消除了物料清單中表現為可編程邏輯的額外芯片的必要性。另外,相對于霍爾效應傳感器,ADC正弦濾波器組合的隔離還具有線性度更佳的額外優勢,有利于減少諧波失真。

隨著電網智能化步伐的加快,太陽能光伏逆變器將需要具備更多智能,以幫助解決電網不平衡問題。這是指來自多個源的電力超過需求的情況。為此,業界十分重視光伏系統智能,以電網整合為目標,電網的每個供電商必須相互合作以實現電網的穩定。電網整合要求更好地對饋入電網的電能進行測量、控制和質量分析。一種專門為電網電力質量監控而設計的諧波分析引擎有助于滿足該需求。通過計算幾個變量(包括諧波失真、功率、rms電壓、rms電流、VAR、VA和功率系數,可以實現對電力質量的監控。用于執行這些計算的專用引擎不但可以帶來超高的精度,同時還能減輕ARM Cortex-M4內核的負擔,使其無需執行該任務。

利用在設計時充分考慮了這種最終應用的混合信號控制處理器,太陽能逆變器可以在系統層面獲得極大的優勢。基于對市場趨勢的了解以及堅實的系統知識,可以打造出智能化集成芯片,這種芯片不但能支持新一代拓撲結構,減少芯片數量,同時還能帶來更多功能以支持與智能電網的接口。

在關于發電方式的環保擔憂之外,人們還十分關心能源的使用效率問題。鑒于電機占全球用電量的40%,所以問題是如何提高這些系統的環保性。答案在于提高其效率,由此減少能耗。通過普及高效電機而節省的能源量十分可觀:每年可節省數千億千瓦時的用電量,可減少大氣中二氧化碳排放量數百萬噸。顯然,高效電機的影響具有十分重要的意義。

具體地,有多個關鍵因素推動著高效電機的應用。其中一個是環保問題推動的政府立法。歐盟已經實施相應的法規,將來還會實施更多法規,強制要求使用更高效的電機系統。另一個關鍵推動因素是全壽命成本優勢。在電機控制系統的成本中,材料約占15%,運行所用能源成本占85%.可見,通過提高效率,降低電機系統全壽命成本的潛力是非常巨大的。

提高效率的方式包括特別的電機設計,電機類型的選擇,為不具備這種控制的系統添加可調速驅動器(ASD),以及針對效率而優化的控制算法。就特別的電機設計和特定電機類型的選擇而言,永磁電機一直是關注重點,其使用呈增長之勢。永磁電機的效率最高可達96%,超過了歐洲超高效能效標準(IE3)。

智能集成式混合信號控制處理器有可能實現ASD和控制算法的改進。以成本優勢明顯的方式集成基于ARM的CPU子系統、PWM、ADC和多路復用功能,結果可以在系統層省去ASD的物料成本。

利用轉換時間較快的高精度ADC,可以改進控制算法。結果可增進電機系統的總體效率。精度高于12位的ADC可提高精度,用其來控制相位電流。然而,不能用采樣轉換延遲控制來換取更高的精度。這樣就不能選擇通過均值或過采樣方式提升SNR的ADC.需要以終端機器(比如,貼片機)

的運動速率來測量變量。快速轉換時間,加上快速ARM微控制器內核,可以加快控制環路的運行速率,改進響應時間,縮短建立時間。反過來,這又能提高生產線系統的吞吐量和效率,從而降低生產成本。

就如太陽能光伏應用一樣,SAR ADC是電機控制的良好選擇。在電機控制的例子中,可以設計出高性能SAR ADC,無需均值或過采樣也可達到要求。

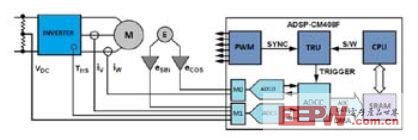

圖3中的各種知識產權模塊都經過精心設計,相互配合良好。需要的結果是一種高度敏捷的儀器儀表子系統,可以采集多個計劃精確的采樣,并高效地將其交付給ARM的主存儲器。對于電機控制,相位繞組電流和其他測量值均可在PWM周期中的精確指定點進行同步采樣。在此基礎上,采樣數據可以在不產生開銷的情況下高效地移至微控制器的存儲器以進行處理。為了實現這一目標,混合信號控制處理器中有5個不同的模塊需要協同工作。

圖3.電機控制系統功能框圖

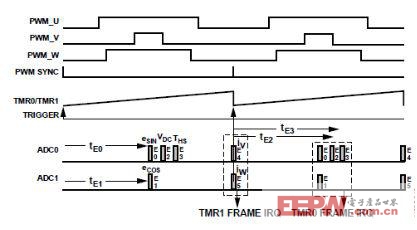

周期開始時,發送一個PWM脈沖到觸發路由單元(TRU),后者負責將觸發主機連接至觸發從機。在本例中,PWM為觸發主機,ADC控制器(ADCC)定時器為觸發從機。ADCC需要具備管理大量事件的能力,并使用定時器(TMR0/TMR1)來跟蹤從PWM觸發到啟動特定ADC事件所需時間。在定時器與特定事件相匹配的情況下,選擇的是ADC輸入多路復用(M0和M1)和通道(ADC0和ADC1)。接下來,將轉換開始信號發送至ADC.采樣數據從ADC移至ADCC,然后從ADCC通過DMA移至微控制器SRAM.

下面的圖4所示為PWM脈沖、PWM同步和ADCC所控制ADC事件之間的相對時序。

圖4.用ADC對5個不同電機控制變量進行采樣的時序

對于面向電機控制的混合信號控制處理器設計,其在PWM、TRU、多路復用、緩沖、SAR ADC和DMA

方面有著良好的知識產權基礎。然而,為了在PWM周期中實現ADC采樣的精密時序,必須對這些模塊的設計進行特別的改動。ADCC模塊的必要性是有事實依據的,即其他知識產權模塊集成于單枚芯片中,它們之間需要協調。ADCC即專門針對這一要求而設計,充分發揮了兩個ADC引擎的高速優勢,這些ADC引擎的轉換時間快達380 ns.

評論