基于晶體管圖示儀的CPLD控制器設計

晶體管圖示儀是電路設計中常用的電子儀器,它能夠顯示晶體管的輸入特性、輸出特性和轉移特性等多種曲線和參數。它不僅可以測量晶體二極管和三極管,還可以測量場效應管、隧道二極管、單結晶體管、可控硅和光耦等器件。但傳統的晶體管圖示儀存在著電路復雜,體積龐大,示波管的顯示屏小,功耗大,價格昂貴等缺點。隨著計算機軟硬件技術、單片機技術和EDA技術的不斷發展及其在電工電子測量技術的應用,晶體管圖示儀在結構、工作原理和功能上發生很大變化,成為數字化和智能化的虛擬儀器。本文設計的晶體管圖示儀就是這樣一種新型儀器,除改善了原有儀器不足之外,還擴展了儀器功能,具有圖形保存,數據處理,界面顯示靈活,可操作性強,性能價格比高等優點。

本文引用地址:http://www.104case.com/article/256146.htm1 系統結構框圖

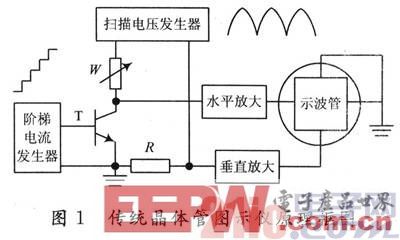

1.1 傳統晶體管圖示儀結構及工作原理

在傳統的晶體管圖示儀中,各模塊單元完全由模擬電路和脈沖數字電路組成,屬于全硬件結構,如圖1所示。它主要包括階梯電流發生器、掃描電壓發生器、垂直放大、水平放大和示波管等。圖中W是負載電阻,R是電流采樣電阻,T是被測三極管。所謂三極管輸出特性曲線是:在基極電流不變的條件下,集電極電壓和電流之間的關系。在測量三極管輸出特性曲線時,階梯電流發生器對T的基極施加階梯電流信號,在階梯電流的每一個臺階時間內,掃描電壓發生器對T的集電極回路施加掃描電壓。掃描電壓是 50 Hz交流電經整流得到。T的集電極電流在采樣電阻R上的壓降(代表集電極電流)經垂直放大后加到示波管垂直偏轉板上,T的集電極電壓經水平放大后加到示波管的水平偏轉板上。當施加的階梯電流和掃描電壓周期性地重復出現時,三極管輸出特性曲線就可以顯示在示波管上。

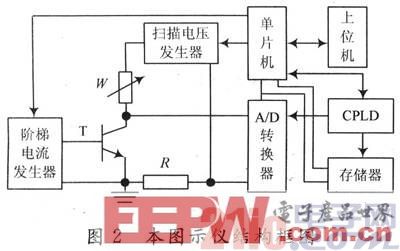

1.2 本圖示儀結構框圖

本圖示儀的構成見圖2。與圖1相比不同的是:“垂直放大”、“水平放大”和“示波管”取消了,其功能由上位機承擔;同時增加了單片機、CPLD、存儲器和 A/D轉換器等部件,組成數據采集電路。工作時上位機向單片機發出數據采集命令,單片機通過階梯電流發生器對T的基極施加階梯電流信號,通過掃描電壓發生器對T的集電極回路施加掃描電壓;與此同時,CPLD控制器控制A/D轉換器和存儲器快速采集和存儲電壓電流數據。當存儲器數據存滿后,CPLD控制器向單片機發出采集結束信號,單片機再將存儲器中的數據通過串口傳送到上位機進行處理和顯示。一個完整的圖形需要多次這樣的過程才能實現。

該系統若不使用CPLD和存儲器等器件也可實現數據采集,但由于單片機工作速度相對較慢,在有限時間(掃描電壓的上升段,5 ms)內采集的點數較少,曲線不夠準確。使用了CPLD和存儲器之后,采得的點數密集,曲線更加真實。本系統的關鍵是設計CPLD控制器,以解決單片機、存儲器和A/D轉換器之間的時序配合關系。

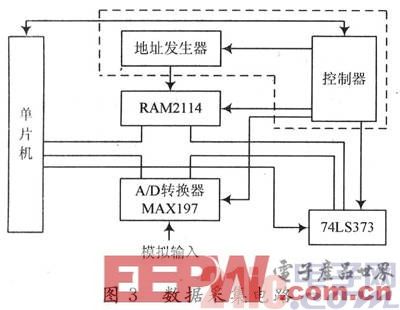

2 數據采集電路功能模塊確定

數據采集電路的構成如圖3所示。除了包含單片機、控制器、存儲器、和A/D轉換器外,還有地址計數器和數據鎖存器。

2.1 A/D轉換器和數據鎖存器

A/D轉換器是數據采集電路重要的部件之一,本系統的A/D轉換器采用Maxim公司的MAX197。

MAX197 是一款多量程的12位A/D轉換器,8路模擬信號輸入,輸出數據線8條,分為高4位和低8位輸出,由HBEN端控制。當時鐘頻率為2 MHz時,轉換時間為6μs。MAXl97在啟動轉換時,需要輸入一個8位控制字,這個控制字若由單片機提供將使啟動時間延長,難以提高采集速度,所以這里用到一個數據鎖存器74LS373來保存控制字。

2.2 存儲器和地址發生器

存儲器采用兩片2114,它是一款4 b×1K靜態隨機存儲器。2114在存取數據時,除了需要外部提供片選信號和讀寫信號外,還需要提供地址信號。地址信號由地址發生器產生,地址發生器實際上是一個計數器。

2.3 控制器

控制器是數據采集電路的核心,由CPLD內部模塊實現。這里的CPLD選用Altera公司的EPM7064。EPM7064有64個宏單元,1 250個可用門類,36個I/O腳。從可行性方面來說,RAM、地址發生器、74LS373和控制器都可以同時做到CPLD中,但RAM需要100個節,用CPLD來實現將占用大量資源,僅一片EPM7064就不夠用。所以為了節省資源,降低成本,這里采用外接RAM2114。74LS373也采用外接方式,主要是考慮端口不夠用。因此在CPLD內部僅安排了控制器和地址發生器(圖3虛線框內)。

3 控制器結構設計

3.1 采集點數的確定及控制器接口要求

晶體管特性曲線中,輸出特性曲線是最復雜的。輸出特性曲線一般由8~10條線組成。在本系統中,每條線由50個點連接而成。每個點由一個電壓值和_個電流值確定,每個電壓(或電流)數據占兩字節存儲單元(數字量12位),則每條曲線的電壓值(或電流值)就占100個字節。電壓值和電流值本應該在同一時刻采集,但為了節省A/D轉換器和其他硬件,這里把電壓和電流安排在不同的掃描周期內采集,只要采集時間與各自的掃描周期起始時間間隔一一對應就可以保證精度,時間誤差在1μs之內。

每一組電壓或電流數據的采集都是在一個掃描電壓的上升時間段完成。掃描電壓是把50 Hz交流電壓經整流產生,所以每個掃描電壓所占時間是10 ms,掃描電壓的上升段時間就是5ms。如果5 ms時間內要采集50個數據,則每個數據占用時間為100μs。10條曲線將占用20個掃描周期。

在每個數據采集時間(100μs)內,控制器首先從鎖存器74LS373中讀取“控制字”送入A/D轉換器,啟動A/D轉換器工作,進入轉換等待狀態。當轉換結束時,控制器從A/D轉換器分別讀取數據的高字節和低字節存入RAM中,然后等待下一個采集周期。待50個數據采集結束后,控制器向單片機發出采集結束信號。所以控制器要產生74LS373的讀信號、A/D轉換器的片選和讀寫信號、存儲器片選和讀寫信號、地址發生器的時鐘和清零信號等,還要接受單片機的采集指令信號和50 Hz交流電同步信號,返回單片機采集結束信號等。

光耦相關文章:光耦原理

可控硅相關文章:可控硅工作原理

手機電池相關文章:手機電池修復

晶體管相關文章:晶體管工作原理

存儲器相關文章:存儲器原理

負離子發生器相關文章:負離子發生器原理 塵埃粒子計數器相關文章:塵埃粒子計數器原理 晶體管相關文章:晶體管原理 離子色譜儀相關文章:離子色譜儀原理

評論