同步控制和即時DSP的先進混合訊號測試

由于IC制程和設計技術的進步以及對于晶片功能和效能的需求,使得目前IC的功能性、效能和速度大幅提升。由于系統的周邊功能越來越多樣化,因此元件也變得越來越復雜。同樣的趨勢也發生在處理類比和數位訊號的混合訊號元件。

為了像系統一樣地測試混合訊號元件,元件的類比和數位輸入和輸出訊號必須具有彈性同步化的功能。此外也需要非同步訊號來模擬實際元件的操作。測試機本身必須能夠產生和測量高解析度的訊號[1][2]并進行快速可靠的測試。針對復雜訊號的產生和量測,即時測試訊號的序列控制可以有效地縮短測試時間。

在本文中,藉由具有同步時脈的復雜序列控制的分割直方圖法(divided section linaer histogram method),可以達到比傳統類比量測更快速且正確的的高解析度ADC(Analog to Digital Convertor, 類比數位轉換器)測試。此外,藉由即時序列控制的分散數位訊號處理(DSP)測試架構可以達到快速測試來解決復雜混合訊號測試的問題。本文以具有特定閃爍的ISDN 2B1Q訊號和行動通訊的PI/4-Shift-DQPSK基頻元件的向量誤差量測為例來驗證即時DSP架構的復雜測試功能。

混合訊號元件模型

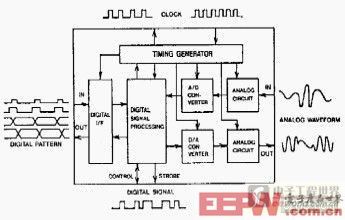

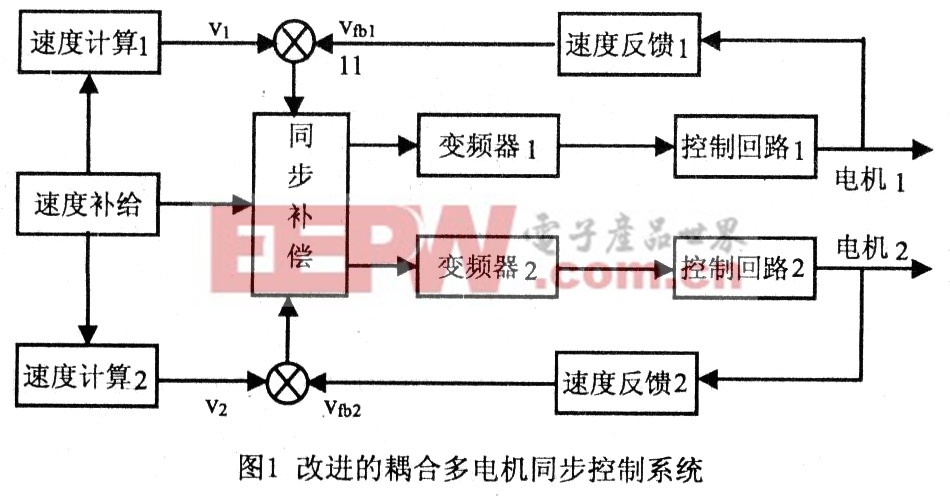

為了解決混合訊號元件測試的要求和問題,我們定義了混合訊號元件測試所需要的同步和非同步控制的通用模型。圖1是混合訊號元件測試的通用模型。

|

圖1:混合訊號元件的通用模型

這個通用模型假設混合訊號測試機具備產生元件測試所需要的各種頻率和時脈關系的能力以及同步不同訊號序列的能力。由于這些訊號會在元件中進行處理元件而輸入或輸出會以相同或不同的方式,因此測試機必須具備彈性來控制這些訊號以符合元件的操作特性并有效地控制測試設備進行快速測試的能力。

測試機架構

在本文中我們開發出符合上節所提到具備同步和非同步控制的混合訊號測試機。

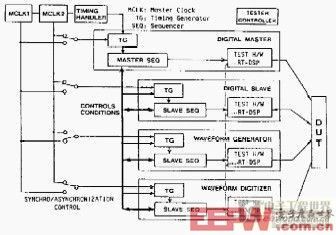

圖2測試機的時脈區塊圖和即時波形控制。測試機的主要硬體元件分成:

供應時脈每個次系統的主時脈次系統(master clock subsystem);產生和擷取數位訊號的兩個數位次系統;藉由任意波形產生器(Arbitrary Waveform Generator, AWG)產生類比訊號的波形產生器次系統;擷取類比訊號的波形數位化次系統(waveform digitizer substysterm)。用來直接與DUT(Device Under Test)介面進行從屬序列控制(slave squencer control)的ADC次系統(未圖示于圖中)。由測試機控制器(CPU)下載的測試程式的程序會執行在每個次系統的控制和資料記憶體。訊號可以在不干擾測試機控制器的情形下藉由浮動接地(floating ground)的光學介面產生和測量訊號而次系統間的訊號則由平衡線(balanced lines)傳輸以避免雜訊的影響。此外,在即時序列控制時每個測試設備具有一個高效能32位元浮點運算的DSP單元并與資料傳輸路徑連接。具彈性的程式讓DSP可以符合復雜的通訊元件測試所需要的復雜測試訊號和資料流。

|

圖2:先進測試系統架構

測試系統控制

每個次系統是以兩個主時脈的時脈控制方式來進行操作,主時脈可以鎖定元件的時脈輸出因此可以進行個別的頻率設定。這種雙主時脈架構在次系統間提供同步和非同步的時脈控制。在產生和測量不同訊號之前,會先由測試機的控制器中下載程序。并由每個硬體模組序列控制器控制執行的序列,序列控制器根據時脈產生器的時脈來控制混合訊號。混合訊號間的控制是以階層式的主/從序列架構來進行。測試機與元件數位控制電路介面的數位次系統的序列作為主序列而與其他硬體模組的序列作為從屬序列。

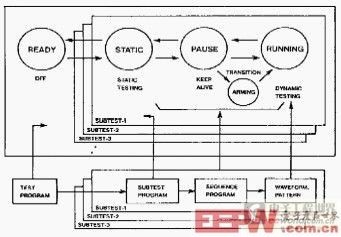

測試機對應實際測試項目的五種測試狀態如圖3:READY、STATIC、PAUSE、ARMING和RUNNING,狀態之間的改變由測試機的控制器控制。在測試程式的開發方面可以使用整合性的工具軟體來簡化開發流程。

RUNNING狀態主要是產生和測量混合訊號,PAUSE狀態讓測試機的控制器可以在維持DUT操作的條件下,也就是不需要中斷混合訊號的產生更改硬體模組設定。這項功能對于除錯時的操作很有幫助。圖4是混合訊號的波形。

|

圖3:測試系統的狀態控制

|

圖4:混合訊號的波形范例

因此,相對于傳統測試數位元件所面臨的問題,這種測試機提供接近工作環境所需的精確非同步訊號輸入和輸出以及測試的簡便性。硬體模組可以輕易地產生和測量不同訊號,每個硬體模組針對I/O埠都可以提供同步和非同步時脈關系的序列功能。這些功能也可以延伸到多DUT的測試以改善測試速度,因此可以平行測試相同或不同的DUT或是平行進行DUT 不同功能的測試。

高解析度 ADC 測試

通常高解析度ADC的小線性誤差必須使用昂貴的測試設備以低測試速度來進行量測。由于DUT的低反應速度和大量的測試序列碼使得測試時間非常長。因此這些元件的測試成本非常高。如果使用稱為分割直方圖法(divided section linear historgram mehthod)[5]的線性直方圖法,可以得到高準確度的高解析度ADC測試結果。使用線性直方圖法的系統架構可以比傳統使用微處理器控制的DVM(Digital Volt Meter)的類比量測減少約十倍的測試時間。分割直方圖法將整個測試ADC的范圍分割成不同的部分,然后施加具有DC偏移值(DC offset)的上升波形(ramp waveform)給每個部分。這個方法可以降低測試設備的線性需求。

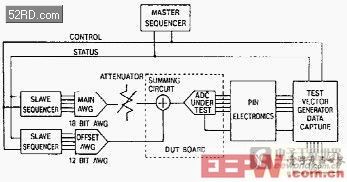

分割直方圖法中會施加16位元的50KHz ADC訊號。圖5是這個測試架構的簡單區塊圖。

在這個方法中,分割部分的數目會決定測試的準確性,因此是很重要的參數。分割部分的數目也必須符合線性的要求,分割部分的數目可以用下式來表示:

n≥2(a-s)хEs/Er 公式(1)

n:分割部分的數目

s:測試設備的位元數目

a:測試ADC的位元數目

Es:在LSB測試設備的線性誤差

Er:在LSB ADC測試的測試準確性

|

圖5:ADC測試的區塊圖

但是,分割部分的數目除了由上式(1)所決定之外還必須考慮測試的解析度。根據直方圖法,測試解析度是由輸入訊號的slewrate和測試ADC的轉換時脈頻率所決定。通常由AWG或測試設備所產生的輸出訊號并不是一個理想的上升波形而是呈現階梯狀的波形。因此測試設備上升波形的slewrate可以用(2)表示如下:

Ss=DsxfsxFs/2S 公式(2)

Ss:測試設備上升波形的slewrate(V/sec)

Ds:在LSB上升波形每個步驟的差值

fs:測試設備的轉換時脈頻率(Hz)

Fs:測試設備的測試范圍(V)

|

圖6:上升暫態波形

|

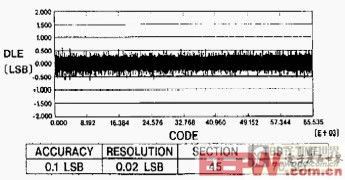

圖7:差額線性測試結果

另一方面,符合測試解析度的slewrate要求可以表示如(3):

Sr=RrxftxFa/2a 公式(3)

Sr:ADC輸入訊號所需的slewrate(V/sec)

Rr:在LSB所需的測試解析度

fs:ADC的轉換時脈頻率(Hz)

Fs:ADC的全部范圍(V)

上升波形的slewrate必須低于所需的slewrate和分割部分的數目,n為Fa/Fs。由(2)和(3)以及(1)和(4)可以決定分割部分的數目。

n≥2(a-s)хDsxfs/Rrxft 公式(4)

上述中最重要的部分為上升波形和上升波形之間的暫態電流。因此主AWG、offset AWG和資料擷取必須改變序列。測試系統的主序列器可以很精確地處理這些工作。圖6是暫態部分的詳細波形。

在上升波形結束,主AWG傳送條件訊號給主序列器之后,主序列器停止擷取資料并傳送控制訊號給offset AWG和主AWG。這個訊號強迫offset AWG提供下一個偏移值,而主AWO輸出’0’。在AWG使用計時器達到穩定之后,主序列器傳送控制訊號給主AWG重新開始上升并重復擷取資料量測。圖7是16 位元50KHz ADC實際的線性測試結果,測試準確性約為19位元而解析度為20位元(16位元的0.05 LSB)。

|

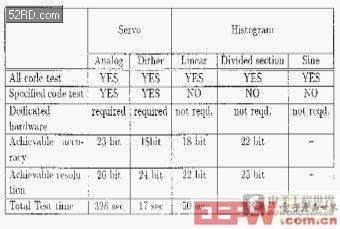

表1

表1是實際經過測試實驗之后所得到ADC測試方法的比較表。分割直方圖法不需要專屬的測試硬體便能達到高解析度、高速以及準確性的ADC測試.

即時DSP應用

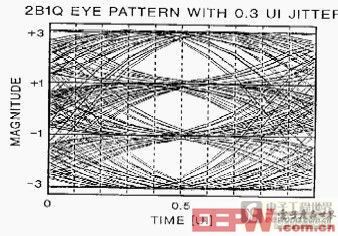

其他復雜的混合訊號應用例還包括如使用即時DSP架構的通訊元件測試。每個測試設備的分散DSP單元可以產生和分析復雜的訊號進行資料處理和計算,而量測訊號則作為測試設備和DUT的介面。圖8是jitter generation的范例。施加ISDN 2B1Q訊號,the可變系數的有限脈沖濾波器(coefficient-variable FIR Finite Impulse Response filter)設計成具有0.0008 UI (Unit Interval)解析度的七階訊號并在AWG產生即時訊號的期間進行操作。

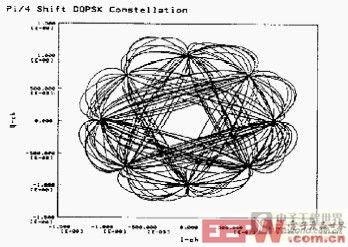

另一個有趣的即時DSP應用例為數位個人手機(Personal Handy Phone,PHP) 基頻元件的PI/4-Shift-DQPSK向量誤差測試。由DUT輸出的I-訊號和Q-訊號使用兩個768KHz取樣速率的數位波形進行測試,這個速率為PHP symbol rate的四倍。I-訊號和Q-訊號的數位資料內差到512倍并在分散即時DSP單元的Root Nyquist濾波器進行處理。圖9是DSP 所形成得單元環的叢集圖。

|

圖8:Eye Pattern with Jitter (0.3 U I)

|

圖9:Pl/4-Shift-DQPSK叢集

|

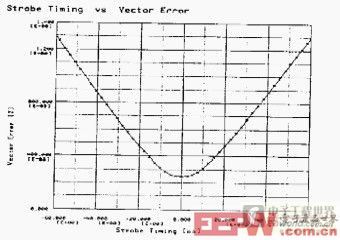

圖10:Strobe時脈和向量誤差

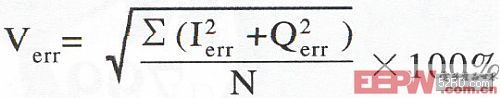

向量誤差定義為叢集的暗區點:

|

公式(5)

基頻元件測試的DUT系統時脈和數位化strobe時脈之間的同步準確性必須小于1%的向量誤差。圖10是量測誤差和strobe時脈偏移的關系。藉由多速率濾波器,即時DSP可以達到0.2 sec以內的向量誤差測試和最佳化的計算點,測試速率會優于專用機。

結論

混合訊號元件測試包括產生和測量各種不同可變頻率的訊號。這些訊號需要復雜的序列控制以符合DUT的測試條件。本文證實雙主時脈和主/從多序列的方式可以在實際操作環境下提供即時控制l的混合訊號復雜且快速的的測試。16 位元ADC的整體線性測試具有20位元的解析度,所使用的分割直方圖法比傳統的類比量測的測試速率快十倍。

因此,分散即時DSP的特性證實可以產生和分析復雜的混合訊號和2B1Q ISDN訊號和PI/4-Shift-DQPSI基頻元件向量誤差測試的操作測試。這種測試機架構可以適用在各種通用的測試機。

評論