利用DFT規則提高ASIC錯誤檢測范圍

本文是作者關于錯誤檢測范圍分析和ASIC設計全掃描測試模擬的第二篇文章(第一篇《在設計中遵循DFT規則提高錯誤檢測覆蓋率》見本刊今年8月第二期)。在前一篇里作者討論了一些實用的方法,系統地分析了未包含在全掃描檢測范圍內的恒定錯誤,并提供設計實例,文中主要講了一些重要的DFT規則,只要遵循這些規則就能大大提高錯誤檢測范圍。本文則詳細介紹如何針對錯誤檢測范圍(而不是邏輯驗證)用錯誤模擬的方法來模擬ASIC非掃描向量,其中的原理同樣可以應用在FPGA等其它IC設計中。

ASIC 供應商們廣泛應用掃描測試來檢測一般稱為恒定錯誤的制造缺陷,錯誤檢測范圍分析的目的是精確計算所有可檢測錯誤百分比,并尋找方法將不在檢測范圍內的錯誤加入到檢測范圍內,以使最終錯誤檢測范圍百分比達到95%以上,這也是ASIC供應商所使用的標準,用以證明電路本身制造是正確的。

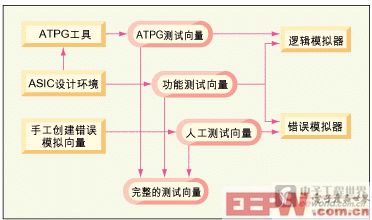

從DFT 規則1(參見《電子工程專輯》2002年8月第二期第46頁《在設計中遵循DFT規則,提高錯誤檢測覆蓋率》一文)可知,我們應該進行邊界掃描,或者在嵌入式RAM周圍增加測試點進行全掃描測試,即需要對設計作一些更改。但假如由于進度、性能或面積等原因不能這樣做該怎么辦呢?如何將非掃描邏輯模塊加入到測試范圍之內呢?因為大多數不可測錯誤很可能就存在于這些模塊中。在這種情況下,一般是進行錯誤模擬,使用一個支持恒定錯誤模型的特殊模擬器(稱為錯誤模擬器),針對錯誤檢測范圍模擬非ATPG(自動測試模式)測試向量。非ATPG向量可以是那些最初開發用于功能驗證的向量,也可以是手工開發用來針對己知錯誤的向量(圖1)。

錯誤模擬不能從零開始,它從ATPG工具提供的錯誤檢測范圍結果中讀出數據,并加上非ATPG測試向量提供的其它錯誤檢測結果。所以讓錯誤模擬器能讀入 ATPG工具的輸出文件非常重要,確保做到這點的方法之一是使用同一供應商提供的兩種工具,如果這兩種工具來自不同的供應商,在購買以前就要確認兩種工具之間可以交流。另外一個關鍵之處是有些錯誤模擬器不能直接使用測試基準程序(如在Verilog中使用的程序),且需要特殊格式的輸入激勵和輸出響應文件,如由1和0組成的二進制格式。

因此需要有一個工具來進行這種轉換,工具可以由ASIC供應商提供,大多數情況下必須使用C、C++或者Perl5之類的語言進行開發,記住要分配足夠的資源用于該項重要任務。

圖1中的功能測試向量由幾個不同類型的測試向量組成,錯誤模擬的第一步是決定哪一類向量能提供最大錯誤檢測范圍,從而只模擬這些向量,其中包括:

·邏輯測試向量 由ASIC設計人員或DVT工程師或共同開發生成,用于對設計進行功能驗證。

·BSR測試向量由ASIC供應商使用BSDL文件創建生成,如果每一個初級I/O引腳都處于邊界掃描鏈中,那么這些向量還包括參數測試向量。

·參數測試向量由ASIC設計人員或DVT工程師或共同開發生成,用于不是每個初級I/O引腳都處于邊界掃描鏈的設計,這種向量使每個初級I/O引腳在狀態1、0和Z態間轉換。

·TAP控制器測試向量由ASIC設計人員或DVT工程師或兩者共同開發生成,用于通過TAP邏輯中每個要求的狀態和掃描指令,并測試邊界掃描邏輯。TAP邏輯有些錯誤可以被掃描測試本身所覆蓋,如那些在時鐘網表中的錯誤,但其它的必須用這些向量進行測試。

經驗顯示,邏輯測試向量對于錯誤檢測范圍不是很有效,因為它們不是專門針對錯誤的,但偶爾它們也會將一些ATPG測試范圍內部或外部的錯誤傳送至初級輸出處。假如把它們放在芯片測試儀上運行,就可以使用錯誤模擬找出這些向量是否恰巧檢測出一些檢測范圍以外的錯誤,如果能夠的話就不必再手工編寫測試向量將那些錯誤歸到檢測范圍之內,但這需要對設計有透徹的理解且要做很多工作。

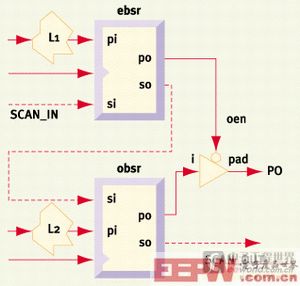

BSR向量很難用于錯誤模擬,原因是ASIC供應商的邊界掃描工具只能讀取BSDL文件,并只根據初級I/O引腳狀態生成BSR向量,它不知道ASIC內部任何邏輯。圖2是兩個BSR組成的一個邊界掃描鏈,用于三態初級輸出引腳PO。

為了在非ATPG測試向量上進行錯誤模擬,應確保模擬器會產生帶有這些向量的預期輸出響應,并且不能有任何不匹配。使用BSR時我們可以從BSR向量中的 TMS信號值算出邊界掃描鏈轉移結束時間,對該時間而不是轉移中的輸出響應進行比較。錯誤模擬器也可以這樣做,但不是自動的(監視TMS引腳數值)。此外,生成BSR向量不需要有關ASIC內部邏輯的知識(我們只對其中的錯誤分類感興趣),所以要大幅增加錯誤檢測范圍不太可能。鑒于這些理由,通常不使用 BSR向量。

錯誤模擬的第二步是了解ATPG和錯誤模擬兩者所得到的錯誤之間的區別,因為后者必須從前者的錯誤檢測范圍結果開始,之所以有區別主要源于下面一些原因:

·RAM BIST模塊在ATPG中作為黑盒模型而在錯誤模擬中卻作為真實邏輯模型,所以錯誤模擬能看到ATPG看不到的所有BIST模塊錯誤,這沒什么關系,只需告訴錯誤模擬器不要針對這些模塊中的錯誤即可。

· 錯誤模擬中使用的網表可能與ATPG中使用的網表不同。例如當ATPG運行時,因為它在后端流程中處于早期階段,所以還沒對設計進行適當優化。設計布局布線完成后,將產生門和網絡延遲,根據這些值,有些門可能要進行充實,甚至需要作少許設計更改,這時既可以在修改過的網表上再運行ATPG,也可以用錯誤模擬覆蓋這些增加的錯誤。注意要將類似這樣的不匹配報告給ASIC設計人員,確保引起足夠重視。

·ATPG測試中掃描觸發器是多路復用掃描型,其clk、d和si引腳是自動測試的(qn引腳不是);而在錯誤模擬中,這些引腳變成邏輯引腳,是錯誤模擬器的檢測對象,必須告訴模擬器不要對這些引腳進行檢測。

·如前所述,如果門級網表使用Verilog賦值語句,ATPG將把它轉換為數據庫中的偽緩沖器單元,而這些單元不在錯誤模擬器數據庫中。

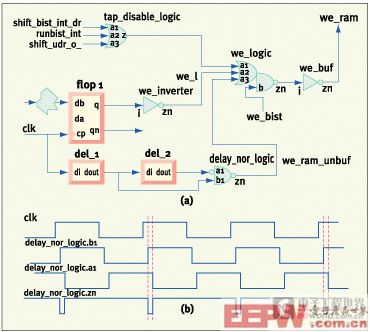

· 有時候僅僅為了錯誤模擬器必須修改設計網表,如在使用延遲單元時。圖3(a)中的del_1和del_2就是這種單元,結果使clk和 we_ram_unbuf信號間的電路及其產生的波形不能在錯誤模擬器中直接進行模擬,這是因為we_ram_unbuf的正確波形依賴于通過兩個延遲單元的延遲信號,但延遲信息是不能模擬的。在這方面不是只有錯誤模擬才這樣,ASIC仿真和測試系統也有同樣的局限。

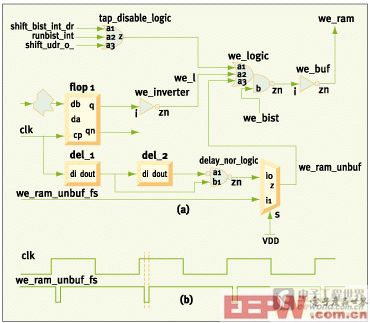

在錯誤模擬中我們所能做的就是旁路掉圖3(a)中clk和we_ram_unbuf信號間的電路,方法是從一個稱為we_ram_unbuf_fs(_fs表示錯誤模擬)的附加初級輸入引腳處將we_ram_unbuf波形直接送至we_logic的a3引腳,如圖4。如果設計里有多個RAM,可將引腳 we_ram_unbuf_fs送至所有這些RAM。注意這個引腳和多路器只是為了錯誤模擬而加上的,并不用在芯片制造中。

總之,你必須了解ATPG和錯誤模擬之間網表的差別,并決定錯誤模擬的對象是什么。錯誤模擬數據庫(包括ATPG錯誤檢測范圍結果)建立好以后,錯誤模擬器就可以創建它所能得到的初始錯誤檢測范圍,這可能與ATPG看到的初始錯誤檢測范圍不同,具體取決于所顯示的新錯誤數量和確定不作為檢測對象的錯誤數量。此外,由于將RAM模擬為灰盒以及測試數據現在可以完全傳送以測試所有直接訪問RAM的非掃描邏輯,錯誤模擬中的不可測錯誤要比在ATPG中少得多。

同樣,非掃描觸發器也不再是指定的ALWAYS0或ALWAYS1模型,事實上有些類型的不可測錯誤完全消失了,如像CONS_UNCNTRL_UNTESTABLE和CONS_UNOBSRV_UNTESTABLE錯誤,這是因為沒有將初級I/O引腳限制為恒定值。

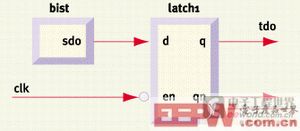

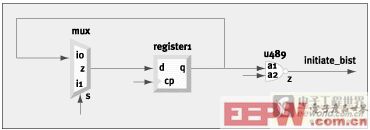

錯誤模擬而不能由ATPG報告,這就是CLOCK_FAULT_UNTESTABLE錯誤。這種錯誤大多產生在存貯單元(觸發器和鎖存器)的時鐘引腳上,不可能對它們初始化,從而使不確定值傳送到輸出端。如圖5中latch1引腳en上的恒1錯誤, CLOCK_FAULT_UNTESTABLE錯誤也產生在非時鐘引腳上,如圖6中mux引腳上的恒0錯誤。

那么在ATPG中這些引腳上會有什么類型的錯誤呢?因為圖6非掃描觸發器 register1指定為ALWAYS0模型,所以mux上所有錯誤都是DANGLING_UNTESTABLE。圖5的latch1在BIST模塊內部而沒有被ATPG看到,因此時鐘和使能引腳上的CLOCK_FAULT_UNTESTABLE錯誤最多變成可能檢測到的錯誤。雖然輸出值是不確定的,但一般它們能在測試儀上檢測到,因為時鐘錯誤最終會產生一個與預期不同的輸出值,所以可從錯誤模擬器中排除這類錯誤。

錯誤模擬的最后一步也是最困難的:將非掃描測試向量翻譯成錯誤模擬器所需的格式。市面上還沒有這類翻譯器,必須得自己寫。

有些ASIC供應商使用一個24-邏輯值系統來描述工作在芯片中的測試向量。例如,如果一個輸入腳得到一個值為“1”的激勵,在整個模擬周期中1都不會變化;如果加在這個引腳上的激勵為“/”,則在當前周期中這個值會從以前的值改變為當前值1,并在當前周期的余下時間里都保持為1。

最困難的問題是將這個24-邏輯值系統與錯誤模擬器所使用的4-邏輯值系統(1,0,X和Z)匹配起來。例如對于一個三態或雙向引腳,如果它的控制信號是X 或改為X,引腳的值可以是24-邏輯值系統中C、E、Z、c、e和z中的一個,但在錯誤模擬中這個值必須是X或改為X。當控制信號是X時就是大多數邏輯和錯誤模擬器工作的方式,如果控制信號不是X,而三態或雙向引腳是C、E、Z、c、e和z中的一個,那么在錯誤模擬中這個值將轉換成Z。必須充分了解這一細微之處并進行正確處理,否則錯誤模擬輸出響應將不匹配。兩個系統之間的另一個區別是,24-邏輯值向量含有用于三態或雙向引腳的內部控制信號,這個信號不能進入到錯誤模擬器使用的激勵和響應文件中,但它們可以告訴翻譯器什么時候三態引腳為Z值以及什么時候雙向引腳改變方向,這樣就能正確生成這兩個文件。

編寫翻譯器的工作量很大,因為兩個系統之間的區別數量大,而且非常細微,但這一點能夠做到而且必須做到。因為錯誤模擬的關鍵是要將內部錯誤的影響傳送至初級輸出以進行觀察,所以我們的目標是測試向量在轉換以及被錯誤模擬器使用時沒有輸出不匹配。即使有一個輸出不匹配錯誤模擬也是無效的,因為這表示模擬向量沒有按芯片在芯片測試儀上進行測試的同樣方法運行。錯誤模擬可以在正確的輸入激勵和輸出響應文件生成后開始,每項測試運行結束后,標出檢測到的錯誤,這樣在后面就不用再對其進行測試了。在這種情況下,每項測試都會減少余下檢測范圍之外的錯誤。所有提供的非掃描測試運行完以后,很可能仍然有一些檢測范圍以外的錯誤。如果這些錯誤所在的模塊必須位于錯誤檢測范圍內,就應針對這些錯誤用手工開發更多的測試向量,這將是一個耗時并需要多次反復的過程,但也可以從很多地方(如錯誤模擬工具供應商處)獲取實用且經過驗證的方法和有用的工具。

總之,掃描測試問題在ASIC設計中不是一個小問題,如果前期沒有充分考慮到,那么到了后期將花費大量的時間和資源。所以很重要的一點是將它們作為與設計相關的事項對待,而不是與設計無關。同樣重要的是,ASIC設計人員應與掃描測試新技術保持同步,因為新技術能以更容易的方法得到更高錯誤檢測范圍,并與現有掃描測試方法配合使用。

評論