航天測控:系統級BIT設計及BIT驗證技術

系統級BIT是監控系統關鍵功能、檢測隔離系統級故障的主要手段和方法,也是可測試性設計的關鍵部分。而系統級BIT相對于板級BIT來說,信息分析工作更加繁雜,需要考慮的因素更加廣泛,因此,單純的采用一種技術和一種結構是遠遠不能達到要求的,必須采用多種關鍵技術相結合使用的方法來進行。

系統級BIT設計技術的主要內容是系統級BIT體系結構技術、智能BIT設計技術,以及降虛警技術。此外,BIT設計技術一個非常重要的環節-BIT驗證環節也不容忽視。BIT驗證就是在研制的產品中注入一定數量的故障,用BIT設計規定的測試方法進行故障檢測與隔離,按其結果來估計產品的測試性水平,并判斷是否達到了規定要求,決定接收或拒收。

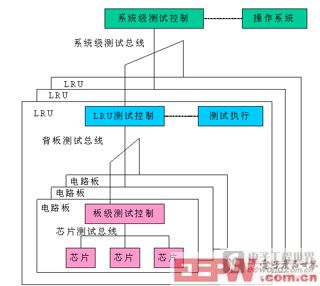

一、系統級BIT體系結構

分散、獨立式的常規BIT結構已經不能適用系統級BIT發展的需要了,因此大型復雜系統中的智能BIT越來越多的采用分布式、集中式和分布集成式的BIT結構。這即是BIT技術長期探索的結果,也是電子系統固有的層次化特點的要求,體現了系統開發的“并行設計”思想。

1、分布式BIT

分布式結構的BIT 是在每個分系統中都具有自己的微程序和微診斷,每個分系統的微處理器只為本系統負責,與其他系統沒有任何關系,各自分系統的微處理器能夠對本分系統的狀態做出判斷和決策最后通過系統故障顯示器顯示系統的狀態。

2、集中式BIT

集中式BIT在每個分系統級均不設置自己的微程序和微診斷,整個系統的控制、診斷、和決策功能都依靠一個微處理器來實現,各個分系統只是將采集上來的信息通過數據總線上傳到這個主微處理器。此微處理器通過分析接收到的數據信息,以及儲存的歷史信息,綜合診斷整個系統的功能狀態,對監測系統進行分析評價,并做出決策,同時將此狀態信息輸出到各顯示裝置并儲存此狀態信息。

3、分布集成式BIT(HIBIT)

所謂HIBIT設計是指所設計的可測試性機制具有同系統一樣的遞階層次結構,即具備包括系統級、子系統級、電路板級、多芯片模塊級和芯片級的層次結構,不同層次的可測試性機制之間通過測試總線相連。實質上,HIBIT技術是邊界掃描技術的一種延伸,在HIBIT中,板級測試利用IEEE 1149.1邊界掃描標準進行,而設備級、系統級的測試則通過IEEE 1149.5 MTM總線進行。

遞階集成BIT

二、智能BIT技術

近20年來,智能BIT技術有了迅速發展.目前已出現了綜合、信息增強、改進決策、維修歷史、自適應和暫存監控等多種智能的BIT 技術。

上述六種智能BIT技術分別針對BIT問題的某個特定方面,運用ES(專家系統)、神經網絡、有限態自動機等AI技術,試圖從根本上改善常規BIT中由于故障診斷算法落后、不能利用人的經驗和維修歷史數據,不能識別設計時未考慮的新的失效模式等造成的虛警、CND和RTOK問題。在實際應用中,可以將它們以各種不同的方式綜合起來,構成范圍更廣的BIT改進方法。比如,一方面,可以在單個分系統中采用信息增強BIT或改進決策BIT來改進BIT效能;另一方面,全部六種方法可以綜合形成一個覆蓋整個系統的智能BIT系統。

三、抗虛警技術

由于BIT診斷模糊性和診斷能力不足造成了BIT虛警率(FAR)高、不能隔離間歇故障等問題,嚴重降低了BIT診斷檢測結果可信度,影響了使用和維修人員對BIT的信任。因此對BIT的虛警問題為重點進行分析和研究,提出一些解決BIT虛警問題的方法和措施,也是目前一個研究重點和熱點。

1、BIT虛警產生原因

導致BIT虛警主要原因可歸納為以下幾個方面:BIT設計上的缺陷、門限值(或測試容差)選擇不當、故障診斷算法不合適、BIT工作可靠性不高。

2、BIT虛警控制

針對BIT上述各種產生虛警原因,進行BIT虛警控制、降低BIT虛警率時,可在BIT的各個階段采取多種方法來實現。

從BIT設計方案中減少虛警 在報警前經過多次判斷或延時報警,以濾除掉瞬間影響;為了減少容差查生的虛警,必須進行合理的可靠性容差設計。利用BIT檢測冗余技術對檢測結構進行故障表決,以減小虛警率;最后還要制訂完善的測試驗證計劃。BIT設計是否滿足要求,必須經過各種測試和驗證等。

進行完善的數字仿真工作 要降低BIT的虛警問題,必須建立完善的系統性能模型,進行故障模式影響分析,以便及時發現設計中的不可靠環節,并采取一定的方法進行故障的消除和隔離。

從硬件上降低BIT虛警問題 通常規定BIT的可靠性比測試系統及設備的故障率要提高一個數量級,一種方法是構成BIT的元件的故障率比系統及設備所彩云的元件的故障率第一個數量級;另一種方法是規定系統中BIT的元件數不多于整個系統電氣元件總數的10%;此外BIT系統自診斷、系統重構級冗余BIT都可提高BIT自身可靠性。另一方面,采取各種濾波措施,進行抗干擾設計。隨著光纖技術的發展,可以采用光纖數據總線,進一步提高系統的可靠性,降低虛警;此外還可提高元器件的可靠性,采用高精度的測試器件,提高裝配質量,完善生產工藝,進行抵抗惡劣環境應力的設計等。

評論