種OTP存儲器片上時序信號產生電路的設計

文中提出了一種片上時序信號產生電路,用于128 Kbit OTP存儲器。該時序產生電路由地址變化檢測(address transition detection,ATD)電路和脈沖寬度調整電路組成,在芯片內部由ATD電路產生脈沖波形,再由脈沖寬度調整電路產生一個寬度適中的時序信號,該信號即可用于存儲器內部時序的控制信號源。例如,將該信號作為控制信號的信號源,可以通過簡單的延時、與、或等操作派生出相應的控制信號,這些信號就可用于控制存儲器內部各個功能模塊,如靈敏放大器,鎖存器等。并且該信號源的有效寬度可以很方便的調整,較傳統的調寬方式好。

1 電路結構及工作原理

1.1 ATD電路

ATD電路實際上是一種邊沿檢測電路。ATD電路探測一個信號或者一組信號(比如地址總線)的狀態,只要被探測的信號中有一根信號發生的翻轉變化,那么ATD電路就會輸出一個脈沖。其輸出脈沖的寬度由ATD電路的參數決定。由于我們要檢測的是地址線的變化,地址線的變化包括從低到高翻轉及從高到低翻轉,因此需要檢測地址線的上升沿和下降沿。

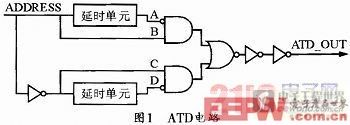

文中所設計的ATD電路能夠檢測地址線上的兩種變化,為雙邊沿檢測電路,電路結構如圖1所示。其中ADDRESS端口為地址信號輸入,ATD OUT端口為檢測電路輸出。

若ADDRESS端的地址輸入無變化,ATD_OUT輸出恒為高電平;

若ADDRESS端的地址輸入有變化,無論從0變為1(上升沿),還是從1變為0 (下降沿),由于延時單元的存在,都會使得到達圖中的與或非門的輸入端A、D的信號比到達輸入端B、C的信號滯后延時單元的傳播延時時間,從而在經過與或非門之后產生一個低電平脈沖,脈沖寬度由延時單元的傳播延時決定。ATD電路的仿真結果如圖4所示。從圖4中可以看出,在輸入ADDRESS端信號的每一個變化的邊沿之后,都會產生一個低電平脈沖信號(圖4中的ATD_OUT信號)。

1.2 脈沖寬度調整電路

由ATD電路產生的脈沖信號,寬度只有2.5ns,并不能直接用于控制內部電路,因為內部的時序控制信號一般要求特定的有效電平寬度。必須先經過寬度的調整,產生寬度符合要求的信號。

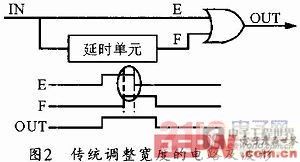

傳統的調整寬度的電路一般采用延時來實現,如圖2所示。E、F分別為輸入波形及經過延時單元以后的波形,OUT為調寬以后的波形,OUT的高電平寬度最大不超過輸入信號IN的寬度的兩倍,因為E和F必須有交疊的部分(如圖中圈起來的部分),否則達不到調寬的目的。這種方式不靈活,假如正好需要兩倍輸入信號IN的寬度的信號,則不好實現。

文中設計的脈沖寬度調整電路如圖3所示。其中ATD_OUT為ATD電路的低電平脈沖輸出信號,EN為使能信號,WOUT為寬度調整以后的脈沖輸出信號。

評論