DDS技術的電磁閥檢測平臺的設計

(2)控制器端程序。

控制器端程序采用Altera 公司CyclONe 系列的FPGA 芯片作為主控芯片。在Quartus II 集成開發(fā)環(huán)境下,采用Verilog HDL 語言進行開發(fā),并利用ModelSim 進行仿真,通過JTAG 電纜將編譯好的程序下載到FPGA 芯片中執(zhí)行。

控制器端程序模塊和實現(xiàn)時采用的主要技術如下:

數(shù)據(jù)接收模塊:此模塊接收PC 端發(fā)送過來的參數(shù),傳遞給信號轉換模塊,并在每個傳送階段結束后計算校驗和。此模塊實現(xiàn)了串口數(shù)據(jù)接收器,利用計數(shù)器對輸入時鐘分頻,采用過采樣和濾波判斷開始位,并使用狀態(tài)機和移位寄存器將串行數(shù)據(jù)轉化為并行數(shù)據(jù)。

數(shù)據(jù)發(fā)送模塊:將數(shù)據(jù)接收模塊計算的校驗發(fā)送給PC 端。此模塊實現(xiàn)了串口數(shù)據(jù)發(fā)送器,由于校驗和的設計,每次發(fā)送給PC 端的數(shù)據(jù)只有1 字節(jié),因此發(fā)送模塊不用使用緩存,簡化了設計。將輸入時鐘分頻之后,采用狀態(tài)機和8 選1 的選擇器便可將并行數(shù)據(jù)轉化為串行數(shù)據(jù),從串行口發(fā)送出去。

信號轉換模塊:轉換從串口接收到的數(shù)據(jù),得到適合顯示控制模塊使用的信號。

顯示控制模塊:根據(jù)所給的圖像數(shù)據(jù)將圖像顯示到電子紙屏幕上。首先將接收到的數(shù)據(jù)存儲在SRAM 中,接收完成后利用參數(shù)將測試圖像顯示在屏幕上。

5 實現(xiàn)結果及分析

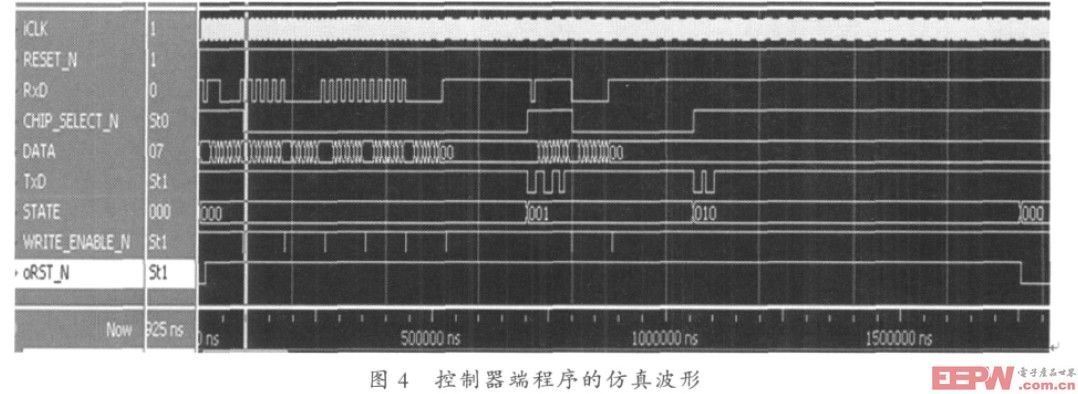

為了驗證通信控制系統(tǒng)與外部接口的接口信號是否正確,利用ModelSim 對程序進行仿真,仿真結果如圖4 所示。

仿真時采用的時鐘頻率為50MHz,為了便于顯示,仿真時將狀態(tài)切換的時間間隔T1 設為50 個時鐘周期,錯誤發(fā)生的時間間隔T2 為狀態(tài)切換間隔的5 倍,仿真串口波特率為115,200bps.由圖可知,開始從串口得到的數(shù)據(jù)為0x07,剛開始收到數(shù)據(jù)時,RST_N 有效,表示數(shù)據(jù)接收開始。當數(shù)據(jù)有效時,CHIP_SELECT_N 信號有效表示接收第1 組數(shù)據(jù),經(jīng)過2 個周期的寫信號延時之后,WRIte_ENABLE_N 有效一個周期。當收到第6 個字節(jié)的數(shù)據(jù)之后,經(jīng)過了T1 的時間間隔,因此狀態(tài)進行切換,CHIP_SELECT_N 無效,此時將通過TxD發(fā)送校驗和。由于總共接收了6 個數(shù):0x07、0x55、0x00、0x55、0x55、0x00,校驗和是0x66,TxD 開始位、數(shù)據(jù)位、停止位依次為0、01100110、1.進入狀態(tài)1 后,收到一個數(shù)據(jù),分析同前一階段。最后,當經(jīng)過T2 的時間間隔,RST_N 信號無效,表明一次傳輸結束或出現(xiàn)錯誤。

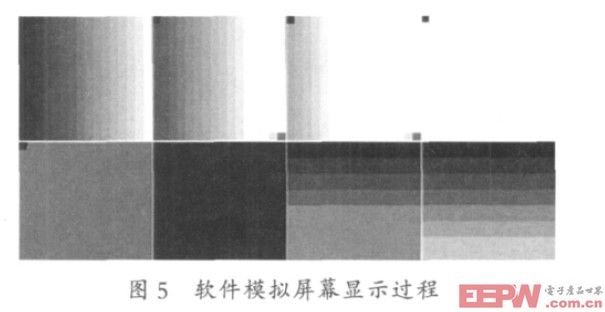

為了驗證前面提出的電泳粒子運動模型的正確性,利用軟件模擬了電泳粒子的顯示過程,采用第2節(jié)中提出的顯示參數(shù)對顯示進行控制。軟件模擬的過程如圖5 所示,該圖顯示了模擬從圖2 的右邊圖像變化到左邊圖像的過程,從圖中可以看到,除了個別顏色的像素外,屏幕首先變?yōu)槿谞顟B(tài),然后變?yōu)槿跔顟B(tài),然后再變化到希望顯示的圖像。由于測試參數(shù)中每兩個色階的控制參數(shù)是一樣的,且沒有考慮到其它因素,因此最后顯示出來的圖像只具有8個色階,總體符合預期效果。

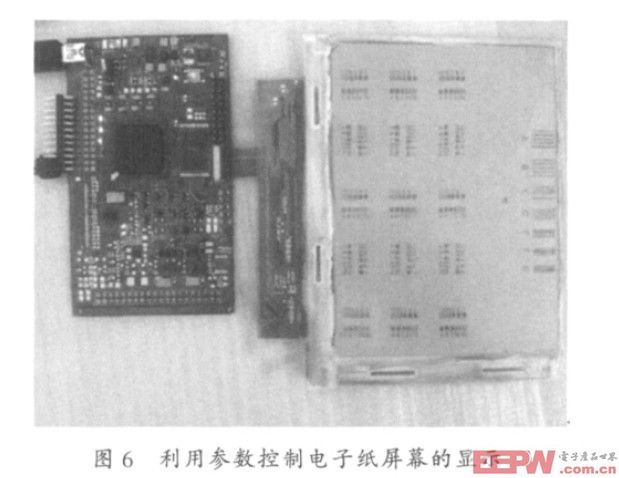

圖6 所示為系統(tǒng)運行的效果圖,利用本系統(tǒng),將ISO12426 標準所需的測試圖顯示在電子紙屏幕上。

利用一些常規(guī)的測量設備,測試出在不同控制參數(shù)下電子紙屏幕顯示的效果,如亮度、分辨率、均勻性等。測試人員通過不斷地改進控制參數(shù),便能使屏幕達到更好的顯示效果。

6 總結與展望

電子紙屏幕的測試對電子紙的顯示性能非常重要,本文分析并設計了電子紙的屏幕驅動控制參數(shù),并設計實現(xiàn)了一個基于PC 的電子紙屏幕測試系統(tǒng)。其可以指導設計開發(fā)時的屏幕參數(shù),縮短開發(fā)周期;指導生產(chǎn)制造時針對一類屏幕的控制方式,改善屏幕的顯示效果。

由于本文設計的電子紙屏幕測試系統(tǒng)采用較為簡單的串口通訊,每次測試花費的時間大約為30s ,速度較慢,未來可以改進為USB 等高速通訊協(xié)議進行通訊,以提高測試速度。另外,目前本系統(tǒng)只能針對黑白屏幕的電子紙進行測試,在以后的研究中可以添加對彩色電子紙的控制與測試手段。

評論