一種射頻收發器的優化方案

4 發射機接口設計和增益計算

對于發射通道設計,ZIF和超外差式架構具有相似的接口特性,均需要在TxDAC?與調制器間執行直流耦合。大多數調制器的中頻輸入電路需要外部提供直流偏置;TxDAC輸出可為直流耦合模式下的調制器提供直流偏置。大多數高速DAC是電流輸出架構,因此需要外輸出電阻才能為調制器產生輸入電壓。

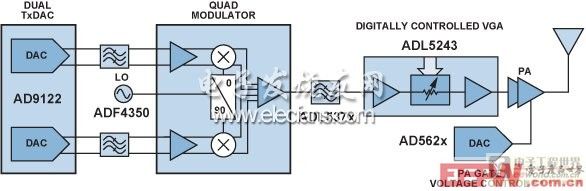

圖5顯示了超外差式或ZIF發射機,該器件采用以下元件:TxDACAD9122、低通濾波器、正交調制器ADL537x、另一個RF濾波器、頻率合成器ADF4350、數字控制VGAADL5243、功率放大器、用于控制功率放大器(PA)柵極電壓的DACAD562x.

圖5.發射機框圖

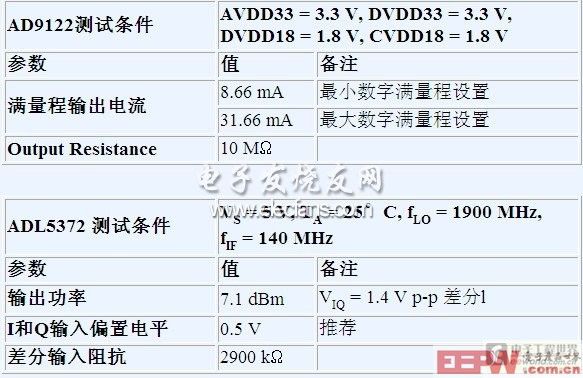

對于AD9122,滿量程輸出電流可設置在8.66 mA與31.66 mA之間。對于大于20 mA的滿量程電流,無雜散動態范圍(SFDR)會變差,但DAC的輸出功率和ACPR也隨著滿量程電流降低而減小。適當折衷的方案是將20 mA交流電流疊加于10 mA直流電平上,得到0 mA至20 mA的電流輸出。

表4.AD9122和ADL5372接口和增益參數

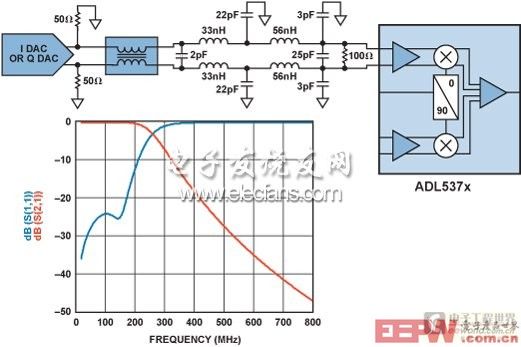

ADL5372的輸入電路需要0.5 V共模電壓,由流經50 Ω電阻的10 mA直流電流提供。0 mA至20 mA交流電流由兩個50 Ω電阻和一個100 Ω電阻共享。因此調制器輸入的交流電壓為20 mA × ((50 × 2) || 100) = 1 V p-p。TxDAC與調制器之間的濾波器用于去除高頻雜散和諧波成分。濾波器的輸入和輸出阻抗為100 Ω。完整接口如圖6所示。

圖6.直流耦合發射機IF接口框圖和濾波器仿真結果

采用50 Ω輸出時,ADL5372的電壓轉換增益為0.2 dBm。使用13 dB PAR調制器信號時,平均功率必須至少減小15 dB,以便適應Tx數字預失真過程。ADL5372具有1 V p-p單音輸入時,平均調制器輸出功率為7.1 dBm – 2.9 dB = 4.2 dBm。如果考慮低通濾波器的2.2 dB插入損耗,平均輸出功率為4.2 dBm – 2.2 dB = 2 dBm。這種狀態下,調制器輸出端平均輸出功率為-10dBm。

為了保證發射鏈路提供11 dBm平均發射功率,Tx信號鏈內后端需要具有26 dBm 的P-1dB的PA驅動器。如果需要2 dB插入損耗的RF濾波器以抑制LO饋通和調制器邊帶輸出,那么增益模塊和PA驅動器必須提供23 dB的總增益。針對此應用,建議使用具有集成式增益模塊、數字控制衰減器和PA驅動器的VGA ADL5243。

5 結語

本文介紹了ZIF和超外差式接收機解調器、IF VGA、混頻器和ADC模擬端口差分設計,以及TxDAC與FMOD之間的發射機差分接口,其中均使用ADI器件作為信號鏈有源部分。另外還提供了設計用于這些電路的應用濾波器的增益計算和仿真結果。

評論