如何用FPGA構建IP監視攝像機的參考設計

目前的視頻監視市場在發展過程中遇到了很多要解決的難題,包括從模擬到數字攝像機的過渡、轉換到高清(HD)視頻、應用寬動態范圍(WDR)傳感器,以及實現進行數據傳輸和控制的互聯網協議(IP)鏈接等。針對這些問題,本文介紹了如何采用FPGA構建IP監視攝像機的參考設計,展示了怎樣采用低成本AlteraCycloneIIIFPGA構建完整的系統。

引言

在視頻監視市場領域,對更高質量視頻、高分辨率以及靈活性和功能的需求促進了從模擬到數字攝像機的過渡。在定義上,高清(HD)視頻必須是數字的,因此,采用HD標準也就意味著過渡到數字傳感器。HD視頻標準支持更高的幀速率和分辨率,需要H.264等新壓縮方法,促使攝像機具有更強的處理能力。

在各種照明條件(強光和暗光、強對比度)下都要求能夠提取出所有圖像內容,因此,數字攝像機采用了新一類WDR傳感器,攝像機也要求在數字域中實現動態范圍壓縮。攝像機中數字數據通路的另一優點是可以在攝像機內部進行“分析”處理。

IP監視攝像機參考設計

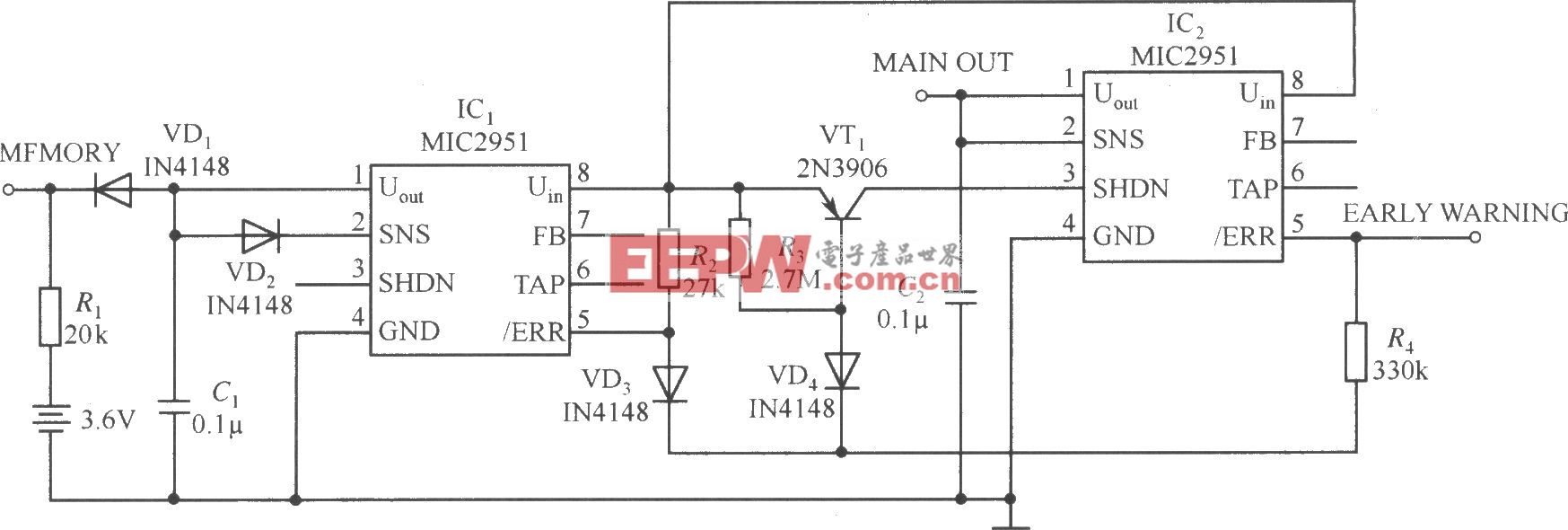

IP監視攝像機參考設計的頂層結構圖和硬件,它主要面向新一代HD(>1MP)WDR傳感器。IP監視攝像機參考設計結合了Altera以及多家合作伙伴的硬件和軟件知識產權。圖1.IP監視攝像機參考設計結構圖。

參考設計的硬件平臺,基于CycloneIIIEP3C120開發板。AptinaWDR傳感器像素數據被送入Apical的圖像傳感器流水線(ISP)。輸出數據是YUV4:2:0格式,寫入到外部DDR2SDRAM的幀緩沖中,它使用了Altera視頻和圖像處理(VIP)套裝提供的組件。然后,使用EyeLytics提供的內核,以H.264格式對視頻數據進行編碼,支持(在這一應用中)3級基線/主要類視頻流,通過以太網在遠程主機上觀看。散射收集直接存儲器訪問(SGDMA)控制器支持Altera三速以太網(TSE)MegaCore?功能,將編碼后的視頻流通過以太網傳送到遠程客戶端。圖2.IP監視攝像機參考設計硬件

寬動態范圍傳感器

AptinaMT9M033是0.33"720p60WDRCMOS傳感器,主要用于監視攝像機市場。傳感器和鏡頭組合安裝在“頂板”上,通過I/O轉換板將其連接至CycloneIIIEP3C120開發板。圖像傳感器流水線CMOSWDR傳感器沒有片內圖像流水線處理功能,以RAW/Bayer格式輸出圖像數據,每像素為20比特。可以采用下式來計算傳感器輸出的大量原始數據:20比特/像素x(1280x720)像素/幀x60幀/s=>1Gbit/s由于數據量過大,因此,很難將新一代WDR傳感器連接至監視解決方案中經常使用的ASSP。因此,FPGA是高效處理數據的理想選擇。Apical的ISP包括以下功能:

■去除熱點像素,抑制噪聲(提供空間和時域IP內核)。

■使用Apical獲獎的專利IridixIP內核實現單位像素高級色調映射功能

■高級去馬賽克和顏色校正

ISP輸出可以作為參考設計的一個選項,通過BitecDVI輸出電路板連接至CycloneEP3C120開發板的第二個HSMC連接器(顯示在圖2的左側硬件中)。

視頻和圖像處理套裝

AlteraVIP套裝匯集了MegaCore功能,設計人員可以利用它方便的開發定制視頻和圖像處理設計。VIP套裝含有MegaCore功能,從顏色空間轉換等簡單的構建模塊功能到可編程多相縮放等復雜的視頻縮放功能。這些功能適合用在多種圖像處理和顯示應用中,例如視頻監視、廣播、視頻會議、醫療和軍事成像等。

在IP監視攝像機參考設計中,采用了多種VIP內核進行顏色空間轉換,采用色度重新采樣功能將ISP的RGB編碼視頻轉換為H.264編碼器要求的YUV4:2:0編碼輸入。如圖5所示,內核連接至應用了Avalon-ST視頻協議的Avalon?流(Avalon-ST)接口。使用Avalon存儲器映射(Avalon-MM)接口,Y和C視頻分量被寫入外部DDR2存儲器的幀緩沖。

在H.264編碼之前,跳過視頻間隔幀,在幀緩沖寫入器中,720p60傳感器幀速率被轉換為720p30,而不是將其寫入幀緩沖中。

視頻壓縮

該設計中使用的H.264編碼器是EyeLytics公司提供的IP內核,它針對監視應用進行了優化。這一內核具有很多監視功能,包括多通道支持、恒定質量速率控制、幀內/幀間模式、QPEL、前后關系自適應二進制算法編碼(CABAC)/前后關系自適應長度可變編碼(CAVLC),并且使用了較少的邏輯門。內核同時支持主要類和基線類。

三速以太網MAC

AlteraTSEMegaCore功能結合了10-/100-/1000-Mbps以太網介質訪問控制器(MAC)和1000BASE-X物理編碼子層(PCS),以及可選物理介質附加子層(PMA)。CycloneIIIEP3C120開發板包括10/100/1000base-T和自動協商以太網PHY,其簡化千兆位介質無關接口(RGMII)連接至TSE功能。

Avalon總線架構和DDR2幀緩沖存儲器采用了一塊具有150MHz32位數據總線的外部DDR2SDRAM,由AlteraDDR和DDR2SDRAM高性能II控制器MegaCore功能對其進行控制,它用于應用程序代碼和數據存儲、輸入和輸出幀緩沖以及H.264編碼器的中間幀緩沖。為達到時序和性能目標,Avalon-MM總線架構是75MHz128位寬。Avalon仲裁共享功能應用于連接DDR2存儲器控制器的每一Avalon-MM總線主機,以保證不中斷的高效訪問H.264編碼器的突發數據。整個系統采用了時鐘交叉橋接、定時器和并行I/O等多種標準Avalon組件。

工具流

使用AlteraSOPCBuilder工具,以完整的芯片系統(SOC)來實現IP監視攝像機參考設計。使用SOPCBuilder,設計人員在GUI中設定系統組件,由SOPCBuilder自動產生互聯邏輯。SOPCBuilder產生定義系統中所有組件的HDL文件,然后,頂層HDL文件將所有組件連接起來。在VerilogHDL中生成IP監視攝像機參考設計,而SOPCBuilder能夠同時生成VerilogHDL和VHDL。

ISP和H.264編碼器可以是具有Avalon-MM接口的SOPCBuilder組件,易于集成到Altera具有標準外設的系統中,以及第三方IP和設計人員自己的組件構成的系統中。SOPCBuilder含在AlteraQuartus?II開發軟件中,提供了全面的多平臺設計環境,很容易滿足特殊的設計需求。QuartusII軟件為FPGA和CPLD設計的所有階段提供解決方案:

■設計輸入

■綜合

■布局布線

■時序分析

■仿真

■編程和配置

使用AlteraNios?II嵌入式設計套裝進行軟件開發。基于SOPCBuilder設計中的組件,生成電路板支持包(BSP),包括所有必須的器件驅動程序等。

軟件應用

采用NiosII嵌入式處理器來設置不同模塊中的各種寄存器,同時運行RTP堆棧,傳送壓縮視頻。采用以太網MAC模塊來控制ISP,嵌入式處理器運行Micrium的uC/OSII實時內核、InterNiche技術公司的NicheStack和RTP堆棧,以及Altera參考設計的視頻流應用程序和網絡服務器應用程序。處理器還處理ISP的自動曝光和自動白平衡控制功能。

視頻流應用程序響應H.264編碼器的中斷,重新裝入各種緩沖指針。重新裝入功能使其能夠準備要編碼的下一視頻幀,將剛剛編碼后的幀通過以太網傳送至RTP堆棧,以便繼續傳輸。通過網絡服務器應用程序,支持ISP進行簡單的控制,使傳感器在正常和WDR模式之間切換,使能和禁止Iridix。這種控制功能具有實時顯示ISP的優勢。網絡服務器應用程序還支持對編碼器進行配置,包括比特率和質量等,在CABAC和CAVLC之間進行選擇。

主機軟件

運行VLC媒體播放器(或者類似的)的主機PC用于查看IP監視攝像機參考設計的流視頻輸出。如圖7所示,主機和EP3C120開發套件之間需要的唯一鏈接是以太網電纜。

性能:IP監視攝像機參考設計的性能指標包括速度、延時、功耗和資源利用率。

速度:在CycloneIIIEP3C120I7開發板上實現參考設計時,DDR時鐘頻率為150MHz,足以使用H.264基線類或者主要類來壓縮720p30視頻幀。Avalon-MM總線架構運行在75MHz,H.264編碼器內核運行在150MHz。DDR2存儲器控制器、Avalon-MM總線架構以及H.264內核通過同步半速率橋接進行連接,以減小時鐘域之間的延時。NiosII處理器和TSE的時鐘為125MHz。采用了NiosII/F(快速)版的NiosII處理器,具有8-Kbyte指令高速緩存、8-Kbyte數據高速緩存,并且支持浮點。

延時:從傳感器輸入到ISP,直至H.264編碼器輸出的延時小于兩幀,它主要來自圖像數據的雙緩沖。在對以前的幀進行編碼時總是將新輸入幀寫入存儲器。

功耗:參考設計總功耗包括所有的輔助模塊和I/O的功耗,達到2.7W。表1顯示了參考設計中使用的每一主要模塊的功耗。其余的700mW來自Avalon總線架構、顏色空間轉換和參考設計的I/O附件。

資源利用率:在CycloneEP3C120中實現整個參考設計時,其資源利用率為:

■107K邏輯單元(LE)(90%器件利用率)■410M9K嵌入式存儲器(95%器件利用率)■140個嵌入式乘法器9位單元(24%器件利用率)

靈活性

基于FPGA的體系結構非常靈活,可以進行定制,完全能夠在大家都了解的標準硬件平臺上實現。通過這種靈活性,可以增強和修改系統體系結構,以適應不同的系統需求。由于采用了標準HDL來實現設計,因此,很容易提高攝像機分辨率,增加定制視頻處理功能或者視頻分析引擎。而且,還可以通過以太網進行遠程更新。例如,把新的FPGA編程文件發送至NiosII嵌入式處理器,然后將文件寫入閃存,從而重新配置系統或者改變傳感器和ISP設置。在單片FPGA中集成整個IP監視攝像機參考設計減少了芯片數量,節省了PCB空間。

不需要與外部器件進行通信,從而減少了I/O鏈接,降低了動態功耗,解決了散熱問題。針對個性化需求,使用不同的FPGA圖像(例如,分辨率、幀速率和壓縮選項),在一個系統設計中便能夠支持多種個性化攝像機。通過縱向移植,可以在同一封裝中使用不同邏輯密度的器件。而且,設計可以在任意FPGA上實現,采用開放設計方案使設計人員能夠針對最新的FPGA進行設計,有了更新的FPGA系列后,可以進一步提高性能,降低成本和功耗。

結論

Altera的CycloneIII和CycloneIV系列低成本FPGA解決了目前最新IP監視系統設計人員所面臨的難題。通過IP監視攝像機參考設計,Altera及其合作伙伴提供了從圖像采集到IP包封的全面解決方案,使用集成在AlteraSOPCBuilder工具中的系列MegaCore功能來提供靈活的解決方案,促使產品及時面市。

評論