一種基于CPLD的單片機脈沖信號源設計

單片機產生的脈沖信號源由于是靠軟件實現的,所以輸出頻率及步進受單片機時鐘頻率、指令數和指令執行周期的限制。文中介紹了一種以CPLD為核心的脈沖信號源,脈沖信號源的參數(頻率、占空比)由工控機通過I/O板卡設置,設定的參數由數碼管顯示,這種脈沖信號源與其它脈沖信號發生電路相比具有輸出頻率高、步進小(通過選用高速CPLD可提高頻率及縮小步進)、精度高、參數調節方便、易于修改等優點。

本文引用地址:http://www.104case.com/article/248533.htm1系統組成及工作原理

脈沖信號源電路核心采用一片可編程邏輯器件EPM7128SLC84—10,它屬于Ahera公司MAX7000系列產品,MAX7000系列產品是高密度、高性能的CMOSEPLD,是工業界速度最快的可編程邏輯器件系列,它是在Ahera公司的第二代MAX結構基礎上采用先進的CMOSEEPROM技術制造的。MAX7000系列產品包括MAX7000E、MAX7000S、MAX7000A,集成度為 600~5000可用門,有32~256個宏單元和36—155個用戶I/0引腳。這些基于EEPROM的器件能夠組合傳輸延遲快至5.0ns,16位頻率為178MHz。此外,它們的輸入寄存器的建立時間非常短,能夠提供多個系統時鐘且有可編程的速度/功率控制。

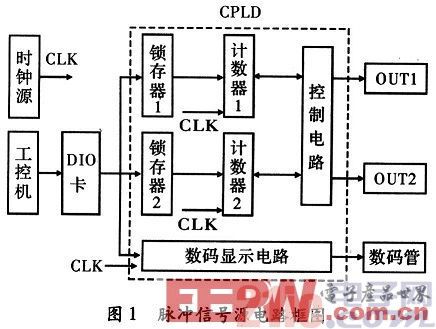

MAX7000S是MAX7000系列的增強型,具有高密度,是通過工業標準4引腳JTAG接口實現在線可編程的,在線編程電壓為5V。EPM7128SLC84—10有128個邏輯宏單元,2500個門電路,8個邏輯陣列塊,68個L/O管腳,速度等級為一6(傳輸延遲 6ns),最高時鐘頻率為147.1MHz。整個信號產生及數碼顯示控制電路(不包括驅動)集成在一片中。脈沖信號源電路由時鐘源、鎖存器、計數器、控制電路、驅動電路以及數碼管動態掃描顯示電路組成,電路框圖,如圖l所示。

時鐘電路采用80MHz有源晶振,它為系統提供時鐘信號;鎖存器1及鎖存器2用于保存頻率及占空比數據,為16位計數器提供預置值,鎖存器位數為8位,設定的數據通過工控機輸入,由于計數器位數為16位,故需分兩次打人數據;計數器1及計數器2作為定時器,按鎖存器1、2 設定的值計時,兩個計數器交替工作,即一個計數器工作而另一個計數器不工作。當工作的計數器到達計時時間后,向控制電路發出時間到信號。控制電路接收計數器發出的信號,停止計數器工作,并重新裝載計時數據,同時啟動另一個計數器工作,從而產生規定頻率、占空比的脈沖信號,并輸出兩路脈沖信號,如圖2所示。為了提高信號源帶負載能力,輸出使用了7417367驅動芯片增加驅動電流。

顯示電路圖,如圖3所示,其中需要顯示的數據代碼通過工控機輸入。緩沖器74LS244用做多路開關,當選通信號有效時,該路鎖存數據有效,數碼管顯示相應的數據。

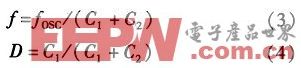

頻率及占空比數據按如下方式計算:

設要輸出的頻率為f,占空比為D,則鎖存器1、2要設定的值分別為

其中fOSC為系統時鐘,C1、C2采用2進制補碼。由式(1),式(2)式可得到頻率及占空比計算式

由上式可以看出信號源最高輸出頻率取決于系統時鐘頻率,最高頻率為系統時鐘頻率的一半(C1、C2均為1),要提高信號源輸出頻率必須提高系統時鐘頻率,既采用高頻晶振或倍頻電路。占空比取決于C1與C1+C2的比值,輸出頻率為最高頻率時,占空比為50%;同樣最小步進也取決于系統時鐘頻率,提高系統時鐘頻率,就可使步進縮小。

如果要信號源輸出頻率為500kHz,占空比為0.5的脈沖波,則按式(1)、式(2)可以算出,C1=C2=HB0(16進制數)。將C1、C2通過工控機置入CPLD中。如果C1、C2為小數,則需取整,取整后需按式(3)、式(4)重新計算頻率和占空比,算出的值為實際的頻率與占空比。

2硬件編程

開發軟件采用MaxPlusⅡ10.2,編程采用VHDL硬件描述語言。

編程采用層次結構,整個程序采用頂層模塊和底層模塊。頂層模塊,如圖4所示。底層模塊包括系統包含的各組件。

整個程序編寫完成后進行編譯、仿真,仿真結果,如圖5所示。編譯、仿真通過后都正確,即可通過JTAG接口將程序下載到目標板CPLD中,目標板即可使用。

3系統控制軟件

系統控制軟件采用LabWindows/CVI編寫,為了給鎖存器置數,可采用如下程序實現:

4技術指標

本脈沖信號源輸出脈沖頻率:20~700kHz,占空比:1%~40%,時鐘采用80MHz有源晶振。在700kHz時頻率步進為6kHz,20kHz時頻率步進為5Hz。

由于采用了EPM7128SLC84—10作為脈沖信號源的核心。電路結構簡單,頻率、占空比可任意設置,準確度高。同時操作簡單方便,功能更易擴展。

模擬信號相關文章:什么是模擬信號

單片機相關文章:單片機教程

單片機相關文章:單片機視頻教程

單片機相關文章:單片機工作原理

塵埃粒子計數器相關文章:塵埃粒子計數器原理 晶振相關文章:晶振原理 脈沖點火器相關文章:脈沖點火器原理

評論