基于AD9852的雷達回波模擬器設計

3 系統設計

本文引用地址:http://www.104case.com/article/246641.htm3.1 系統組成

3.2 工作原理

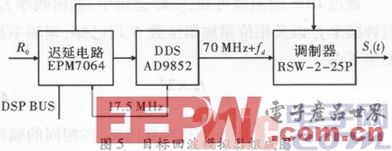

如圖5所示,17.5 MHz基準信號經直接數字頻率合成器(DDS,采用AD9852)輸出70 MHz+fd的目標回波模擬信號,輸出經脈沖調制器(采用MINI公司RSW-2-25P)形成目標回波信號St(t)。控制DSP通過總線(BUS)設置回波信號的遲延和DDS輸出信號的多普勒頻率。

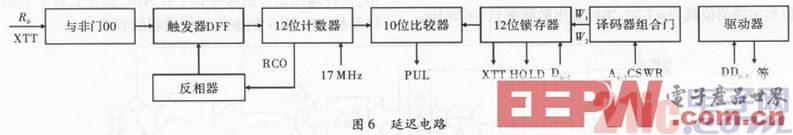

遲延電路組成如圖6所示。XTT=1時電路正常工作,距離同步基準信號R0的前沿使觸發器DFF翻轉,輸出高電平信號令12位計數器退出清零狀態開始對17 MHz時鐘計數。計數值的高10位(T0-9)與10位遲延時間鎖存器的值DE0-9進行比較,二者相等時輸出寬度為0.228 6μs的負脈沖PUL。計數器的進位信號RCO經反相后使觸發器復位。譯碼器對輸入的A6、A7、CS、WR信號譯碼,產生鎖存器的數據鎖存信號W0、W1。XTT信號為0時,電路關閉,無PUL信號輸出。HOLD供AD9852使用,同時對數據總線信號D0-7、WR、RD進行驅動后供AD9852使用。

3.3 系統參數

距離遲延范圍為0.23~233.8μs;fd頻率范圍:+400 kHz;頻率分辨為<5 Hz;衰減控制范圍為>70 dB。

3.4 DDS芯片的優缺點

DDS芯片的優點主要體現在:輸出頻率相對、帶寬較寬頻率轉換時間短、頻率分辨率極高、相位變化連續等。輸出頻率帶寬為采樣頻率的50%。DDS是一個開環系統,無任何反饋環節,這使得DDS的頻率轉換時間極短。若時鐘的頻率不變,DDS的頻率分辨率就是由相位累加器的位數N決定。只要增加相位累加器的位數N即可獲得任意小的頻率分辨率。改變DDS輸出頻率,實際上改變的每一個時鐘周期的相位增量,相位函數的曲線是連續的,只是在改變頻率的瞬間其頻率發生了突變,因而保持了信號相位的連續性。

另外,只要在DDS的波形存儲器存放不同波形數據,就可以實現各種波形輸出,如三角波、鋸齒波和矩形波甚至是任意的波形。由于DDS中幾乎所有部件都屬于數字電路,易于集成、功耗低、體積小、重量輕、可靠性高,且易于程控,使用靈活,因此性價比較高。

DDS芯片存在的缺陷,主要表現在輸出頻帶范圍有限、輸出雜散大。

由于DDS內部數模轉換器(DAC)和波形存儲器(ROM)的工作速度限制,使得DDS輸出的最高頻有限。由于DDS采用全數字結構,不可避免地引入了雜散。其來源主要有3個:相位累加器相位舍位誤差造成的雜散;幅度量化誤差造成的雜散和DAC非理想特性造成的雜散。

4 結束語

在DDS原理的基礎上,提出了一種基于DDS芯片的雷達回波模擬器設計。該設計在實際運用中能夠穩定地產生所需要的回波。而且,由于DDS芯片所具有的優點,使得其簡單方便易于操作。隨著低價格、高時鐘頻率、高性能的新一代DDS芯片問世,它將在更新領域得到更廣泛的應用。

模擬信號相關文章:什么是模擬信號

塵埃粒子計數器相關文章:塵埃粒子計數器原理 鎖相環相關文章:鎖相環原理

評論