德州儀器計劃于2005年第一季度推出采用65納米半導體工藝技術的樣片

TI 首席技術官 Hans Stork 說:“與 TI 成熟的 90納米生產工藝相比,其 65 納米 CMOS 工藝技術使晶體管密度提高了一倍,TI可于明年年初為客戶提供具有65 納米工藝技術優勢的產品,從而確定了TI在該技術領域的領先地位。隨著功能方面的顯著增加,TI提供了采用65 納米工藝技術的高集成度SoC 設計,在產品功耗管理上,我們取得了巨大的進步,在業界處于領先地位。”

隨著多媒體與高端數字消費類電子產品的功能不斷被集成到諸如無線手持終端等產品中,而這些產品通常采用電池供電或對當今極其復雜的處理器所產生的熱量非常敏感,因此低功耗設計成為了 TI 客戶的主要考慮因素。作為解決這一問題總體戰略的一部分,TI 將首先在無線應用的芯片中推出采用 65納米節點的 SmartReflex™ 動態電源管理技術。這種創新型技術將根據用戶需求自動調節電源電壓,有助于控制諸如 TI OMAP™ 應用處理器等器件的功耗。通過使用 SmartReflex 可以仔細監視電路速度,以調節電壓,實現在不降低系統性能的情況下準確地滿足性能要求。因此,可以使用最低的功耗來支持每種工作頻率,從而延長電池使用壽命并降低器件產生的熱量。

采用多方面的方法進行電源管理

TI在半導體制造基礎設施方面投入了巨額資金,并在開發周期的初始就將其工藝技術開發與芯片設計方法緊密結合在一起,以充分利用其在整個產品范圍的專業技術。電源管理僅與以下兩個方面密切相關:半導體工藝技術如何應用于內核晶體管層以及電路設計層。TI的若干種創新技術采用了 65 納米工藝技術,以降低晶體管在空閑時的功耗,如手機來電之前處于待機模式時的這段時間。某些 65 納米創新技術包括 SRAM 存儲區的向后偏置 (back-biasing) 、可使電壓降至極低的保留觸發電路,該電路無需重寫邏輯,以及SmartReflex 電路,其可根據較高或較低電壓的應用要求做出動態響應以提高性能或降低功耗。總而言之,65納米工藝的電源管理創新技術能夠將功耗降低 1,000 倍。

Sun 微系統公司處理器與網絡產品小組的執行副總裁 David Yen博士說:“TI先進的 65納米工藝技術為 Sun 微系統公司奠定了新一代 64 位處理器設計的基礎,以支持我們‘吞吐量計算’計劃及 UltraSPARC™發展策略。除了需具備出色的處理性能之外,功耗也是我們歷年都要評估的重要衡量標準。TI 在電路層及晶體管層均采用了其創新技術,以幫助 Sun 微系統公司在解決芯片及系統級電源管理問題方面始終處于領先地位。”

適用于 SoC 設計的靈活工藝

通過改進90納米工藝以充分利用經濟高效的 CMOS,TI 將提供數種優化 65微米工藝技術的方法,以平衡各終端產品或應用的獨特需求。而這一獨特需求通過調節晶體管的門長度、閾值電壓、門電介質厚度或偏置條件等即可實現。TI 的 65 納米設計庫將為電路設計人員提供眾多無可匹敵的選項,其中包含可最大限度提高設計靈活性與優化性能的多種不同電壓的晶體管。

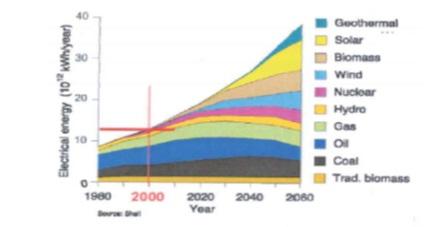

極低功耗的產品將延長諸如 2.5 與 3G 無線手持終端、數碼相機以及多媒體功能日益復雜的音頻播放器等便攜產品的電池使用壽命。中檔產品同時支持基于 DSP的產品以及 TI用于通信基礎設施產品的高性能 ASIC 庫。最高性能的產品(其晶體管門直徑僅為29納米)可支持諸如 Sun 微系統公司新一代基于 UltraSPARC 處理器的服務器等產品。TI最高性能的 CMOS 邏輯器件依賴于門長度極短的晶體管以及高效的門電介質調節能力,以降低電容并提高驅動電流。這些是晶體管開關速度方面的主要因素,它們反過來又決定了處理器的工作頻率。

TI 以 65 納米的工藝技術提供了密度極高的嵌入式 SRAM,其一個單元中的6個晶體管占用面積還不足 0.5 平方微米,并且 1 平方毫米的面積可提供 1.5 MB的內存。極小型 SRAM 單元使 TI 能夠集成大量的存儲器(接近于其處理器內核),從而加速了應用執行進程。此外,SRAM 還是一款非常低成本的嵌入式存儲器解決方案,因為無需額外的制造過程。

充分利用最新材料與制造能力的工藝技術

65納米工藝包括多達 11層與低k 電介質集成的銅互連,該電介質為有機硅酸鹽玻璃 (OSG) ,其k(介電常數)值為2.8。在首次采用130納米工藝進行生產時驗證該材料合格后,TI 就在采用 90納米工藝的整個產品系列上引入了 OSG。低k 材料可以降低電容并縮短器件互連層內部的傳播延遲時間,從而提高了芯片的總體性能。此外,在 NMOS 與 PMOS 晶體管內還集成了其它改進技術,以促使性能提高并最大限度地降低功耗,其中包括:在芯片處理過程中對晶體管通道的工藝應變誘導,以提高電子與空穴遷移率 (hole mobility);用于降低門以及源極/漏極電阻的硅化鎳;以及超淺源極/漏極接面結合技術。差動失調分離器的獨特用途在于其可以單獨對 NMOS 與 PMOS 晶體管進行優化。

模擬與射頻集成

TI 開發資源庫支持眾多不同的閾值電壓晶體管,為了優化電路系統可將這些晶體管組合起來以實現更低的功耗或更高的性能;支持多個包括 SSTL、HSTL、LVDS、DDR II 以及 SerDes的高速 I/O 接口;并支持使用優化模擬晶體管與高密度MIM電容器的模擬/混合信號宏。對于片上系統設計,特別是那些針對注重芯片區域的便攜式系統的設計而言,集成這些模擬功能可以實現更輕便、價格更低、移動性更高的應用。例如,為了在單片解決方案中集成無線電廣播功能,TI的數字射頻處理器 (DRP) 架構充分利用了極快的 CMOS 開關速度及準確的模擬組件。

TI 的 65 納米工藝技術是針對 200 毫米與 300 毫米生產系統而開發的,預計將于 2005 年后期正式投產。將于 2004 年 6 月在夏威夷檀香山召開的 VLSI 座談會上,TI 將展示有關 65 納米低功耗工藝技術的技術資料。

評論