基于TMS320C6202的裝甲戰(zhàn)車智能圖像跟蹤系統(tǒng)硬件平臺(tái)設(shè)計(jì)

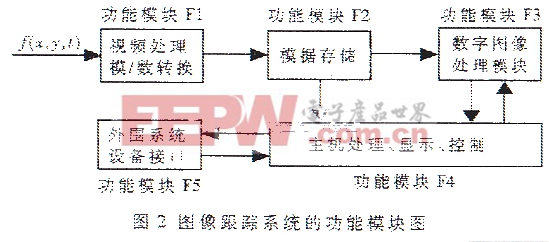

1 系統(tǒng)功能分析 本文設(shè)計(jì)的智能車載圖像跟蹤系統(tǒng)以DSP作為核心處理器,系統(tǒng)構(gòu)成如圖1所示。它首先利用欠采樣技術(shù)進(jìn)行全視場(chǎng)搜索以發(fā)現(xiàn)目標(biāo)或人為指定目標(biāo),系統(tǒng)接收到跟蹤指令和目標(biāo)某一點(diǎn)的坐標(biāo)參數(shù)(x0,y0)后,自適應(yīng)地在目標(biāo)指定位置附近開處理窗;然后利用給出的各種算法對(duì)處理窗內(nèi)的圖像數(shù)據(jù)進(jìn)行處理,計(jì)算出目標(biāo)準(zhǔn)確地位置參數(shù)。在后續(xù)幀的處理中,處理窗的位置由上一幀求得的目標(biāo)位置確定,逐幀處理就可以完成對(duì)目標(biāo)的跟蹤任務(wù)。這樣,系統(tǒng)既能快速進(jìn)行全視場(chǎng)的搜索,又能減小計(jì)算量,提高速度。 為實(shí)現(xiàn)上述基本功能,可將系統(tǒng)功能劃分為幾個(gè)基本功能模塊,如圖2所示。圖3(1) 視頻處理模/數(shù)轉(zhuǎn)換模塊(F1)。它包括視頻信號(hào)的預(yù)處理、A/D轉(zhuǎn)換,即把輸入的信號(hào)轉(zhuǎn)換成系統(tǒng)能夠處理的數(shù)字圖像數(shù)據(jù)。 (2) 數(shù)據(jù)存儲(chǔ)模塊(F2)。將A/D轉(zhuǎn)換出來(lái)的數(shù)字圖像數(shù)據(jù)按照一定的組織形式放在確定的存儲(chǔ)區(qū)域。 (3) 數(shù)據(jù)圖像處理模塊(F3)。運(yùn)用相關(guān)的數(shù)字圖像處理算法實(shí)現(xiàn)目標(biāo)的識(shí)別與跟蹤,該模塊是圖像跟蹤系統(tǒng)的核心。 (4) 主機(jī)模塊(F4)。PC104嵌入式計(jì)算機(jī)在系統(tǒng)中的作用是負(fù)責(zé)協(xié)調(diào)各個(gè)模塊的工作:顯示圖像及跟蹤結(jié)果、執(zhí)行DSP程序加載控制。 (5) 外圍接口模塊(F5)。與系統(tǒng)其它設(shè)備進(jìn)行通信,包括接收用戶輸入、伺服機(jī)構(gòu)控制等。

1 系統(tǒng)功能分析 本文設(shè)計(jì)的智能車載圖像跟蹤系統(tǒng)以DSP作為核心處理器,系統(tǒng)構(gòu)成如圖1所示。它首先利用欠采樣技術(shù)進(jìn)行全視場(chǎng)搜索以發(fā)現(xiàn)目標(biāo)或人為指定目標(biāo),系統(tǒng)接收到跟蹤指令和目標(biāo)某一點(diǎn)的坐標(biāo)參數(shù)(x0,y0)后,自適應(yīng)地在目標(biāo)指定位置附近開處理窗;然后利用給出的各種算法對(duì)處理窗內(nèi)的圖像數(shù)據(jù)進(jìn)行處理,計(jì)算出目標(biāo)準(zhǔn)確地位置參數(shù)。在后續(xù)幀的處理中,處理窗的位置由上一幀求得的目標(biāo)位置確定,逐幀處理就可以完成對(duì)目標(biāo)的跟蹤任務(wù)。這樣,系統(tǒng)既能快速進(jìn)行全視場(chǎng)的搜索,又能減小計(jì)算量,提高速度。 為實(shí)現(xiàn)上述基本功能,可將系統(tǒng)功能劃分為幾個(gè)基本功能模塊,如圖2所示。圖3(1) 視頻處理模/數(shù)轉(zhuǎn)換模塊(F1)。它包括視頻信號(hào)的預(yù)處理、A/D轉(zhuǎn)換,即把輸入的信號(hào)轉(zhuǎn)換成系統(tǒng)能夠處理的數(shù)字圖像數(shù)據(jù)。 (2) 數(shù)據(jù)存儲(chǔ)模塊(F2)。將A/D轉(zhuǎn)換出來(lái)的數(shù)字圖像數(shù)據(jù)按照一定的組織形式放在確定的存儲(chǔ)區(qū)域。 (3) 數(shù)據(jù)圖像處理模塊(F3)。運(yùn)用相關(guān)的數(shù)字圖像處理算法實(shí)現(xiàn)目標(biāo)的識(shí)別與跟蹤,該模塊是圖像跟蹤系統(tǒng)的核心。 (4) 主機(jī)模塊(F4)。PC104嵌入式計(jì)算機(jī)在系統(tǒng)中的作用是負(fù)責(zé)協(xié)調(diào)各個(gè)模塊的工作:顯示圖像及跟蹤結(jié)果、執(zhí)行DSP程序加載控制。 (5) 外圍接口模塊(F5)。與系統(tǒng)其它設(shè)備進(jìn)行通信,包括接收用戶輸入、伺服機(jī)構(gòu)控制等。 2 系統(tǒng)硬件設(shè)計(jì) 下面詳細(xì)介紹系統(tǒng)硬件的總體方案及關(guān)鍵部分的設(shè)計(jì)。 這里提出了一個(gè)以TI公司的TMS320C6202高速DSP為核心并配以嵌入式PC104計(jì)算機(jī)系統(tǒng)的雙CPU主從式實(shí)時(shí)跟蹤系統(tǒng),其硬件結(jié)構(gòu)如圖3所示。 結(jié)合圖2和圖3可以看出:功能模塊F1由硬件單地FS1完成;功能模塊F2由硬件單元FS2完成;功能模塊F3由硬件單元FS3完成;功能模塊F4由硬件單元FS4和FS5完成;功能模塊F5由硬件單元FS5完成;硬件單元FS6完成系統(tǒng)的總線仲裁和邏輯控制功能。 視頻A/D轉(zhuǎn)換芯片選取的是PHLIPS公司的SAA7111A,這是一款增強(qiáng)型的視頻輸入片器,包含兩個(gè)通道的模塊預(yù)處理電路。系統(tǒng)的總線仲裁和邏輯控制電路采用Xilinx公司的大規(guī)模FPGA—XCV50E實(shí)現(xiàn)。通過(guò)一片大容量的FPGA實(shí)現(xiàn)對(duì)所有器件如輸入緩沖FIFO、SRAM、DSP、FLASH編程、PCI接口電路等的邏輯控制。利用FPGA芯片的在系統(tǒng)內(nèi)可編程(ISP)性能,可以使系統(tǒng)硬件的調(diào)試變得非常方便。

2 系統(tǒng)硬件設(shè)計(jì) 下面詳細(xì)介紹系統(tǒng)硬件的總體方案及關(guān)鍵部分的設(shè)計(jì)。 這里提出了一個(gè)以TI公司的TMS320C6202高速DSP為核心并配以嵌入式PC104計(jì)算機(jī)系統(tǒng)的雙CPU主從式實(shí)時(shí)跟蹤系統(tǒng),其硬件結(jié)構(gòu)如圖3所示。 結(jié)合圖2和圖3可以看出:功能模塊F1由硬件單地FS1完成;功能模塊F2由硬件單元FS2完成;功能模塊F3由硬件單元FS3完成;功能模塊F4由硬件單元FS4和FS5完成;功能模塊F5由硬件單元FS5完成;硬件單元FS6完成系統(tǒng)的總線仲裁和邏輯控制功能。 視頻A/D轉(zhuǎn)換芯片選取的是PHLIPS公司的SAA7111A,這是一款增強(qiáng)型的視頻輸入片器,包含兩個(gè)通道的模塊預(yù)處理電路。系統(tǒng)的總線仲裁和邏輯控制電路采用Xilinx公司的大規(guī)模FPGA—XCV50E實(shí)現(xiàn)。通過(guò)一片大容量的FPGA實(shí)現(xiàn)對(duì)所有器件如輸入緩沖FIFO、SRAM、DSP、FLASH編程、PCI接口電路等的邏輯控制。利用FPGA芯片的在系統(tǒng)內(nèi)可編程(ISP)性能,可以使系統(tǒng)硬件的調(diào)試變得非常方便。 2.2 總線仲裁與邏輯控制設(shè)計(jì) 以DSP+PLD方式設(shè)計(jì)的電子系統(tǒng)充分發(fā)揮了DSP在數(shù)字信號(hào)處理方面的優(yōu)勢(shì)和可編程器件在控制邏輯方面的靈活性。 2.2.1 系統(tǒng)總線仲裁方案 系統(tǒng)中的數(shù)據(jù)交換是由總線來(lái)實(shí)現(xiàn)的,因此總線的管理是一個(gè)極為重要的問題。只有恰當(dāng)?shù)匕芽偩€分配給相應(yīng)的總線使用設(shè)備,系統(tǒng)才能穩(wěn)定高效地工作。特別是在一條總線上掛接多個(gè)設(shè)備,并且它們都需要占用總線(即它們都能成為這條總線的主設(shè)備)的時(shí)候,就產(chǎn)生了總線的競(jìng)爭(zhēng)問題。這時(shí)候可以通過(guò)總線仲裁來(lái)解決總線的競(jìng)爭(zhēng)問題。通過(guò)總線仲裁,可以實(shí)現(xiàn)多個(gè)設(shè)備以分時(shí)共享的方式占用一條總線。在總線的仲裁方案中,常常會(huì)指定一個(gè)總線的缺省占有設(shè)備。總線的缺省占有設(shè)備是指缺省狀態(tài)的總線占用者,其它設(shè)備需要使用總線的時(shí)候,可以通過(guò)總線仲裁器向該設(shè)備申請(qǐng)總線的使用權(quán),使用完以后再把總線釋放出來(lái)。 圖4是TMS320C6202的EMIF總線掛接的外設(shè)的示意圖。從圖中可以看出,EMIF接口總線上掛接了以下幾個(gè)設(shè)備:DSP、SRAM、FLASH、邏輯控制電路,其中DSP和邏輯控制電路可以成為EMIF接口總線的主設(shè)備。DSP復(fù)位后,默認(rèn)的狀態(tài)是總線的從設(shè)備,當(dāng)它需要成為總線的主設(shè)備的時(shí)候,就得向外部總線仲裁器(FPGA)申請(qǐng)總線。主計(jì)算機(jī)需要讀取圖像數(shù)據(jù)時(shí),先給FPGA發(fā)送請(qǐng)求,然后FPGA收回EMIF的部線控制權(quán),PCI9054通過(guò)FPGA讀取SRAM中的圖像數(shù)據(jù)。圖5是系統(tǒng)進(jìn)入 正常跟蹤狀態(tài)時(shí)EMIF總線的占用時(shí)序圖。

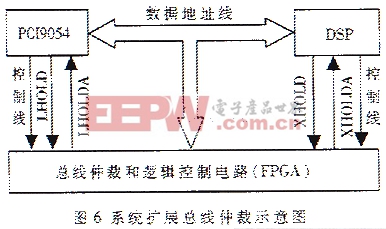

2.2 總線仲裁與邏輯控制設(shè)計(jì) 以DSP+PLD方式設(shè)計(jì)的電子系統(tǒng)充分發(fā)揮了DSP在數(shù)字信號(hào)處理方面的優(yōu)勢(shì)和可編程器件在控制邏輯方面的靈活性。 2.2.1 系統(tǒng)總線仲裁方案 系統(tǒng)中的數(shù)據(jù)交換是由總線來(lái)實(shí)現(xiàn)的,因此總線的管理是一個(gè)極為重要的問題。只有恰當(dāng)?shù)匕芽偩€分配給相應(yīng)的總線使用設(shè)備,系統(tǒng)才能穩(wěn)定高效地工作。特別是在一條總線上掛接多個(gè)設(shè)備,并且它們都需要占用總線(即它們都能成為這條總線的主設(shè)備)的時(shí)候,就產(chǎn)生了總線的競(jìng)爭(zhēng)問題。這時(shí)候可以通過(guò)總線仲裁來(lái)解決總線的競(jìng)爭(zhēng)問題。通過(guò)總線仲裁,可以實(shí)現(xiàn)多個(gè)設(shè)備以分時(shí)共享的方式占用一條總線。在總線的仲裁方案中,常常會(huì)指定一個(gè)總線的缺省占有設(shè)備。總線的缺省占有設(shè)備是指缺省狀態(tài)的總線占用者,其它設(shè)備需要使用總線的時(shí)候,可以通過(guò)總線仲裁器向該設(shè)備申請(qǐng)總線的使用權(quán),使用完以后再把總線釋放出來(lái)。 圖4是TMS320C6202的EMIF總線掛接的外設(shè)的示意圖。從圖中可以看出,EMIF接口總線上掛接了以下幾個(gè)設(shè)備:DSP、SRAM、FLASH、邏輯控制電路,其中DSP和邏輯控制電路可以成為EMIF接口總線的主設(shè)備。DSP復(fù)位后,默認(rèn)的狀態(tài)是總線的從設(shè)備,當(dāng)它需要成為總線的主設(shè)備的時(shí)候,就得向外部總線仲裁器(FPGA)申請(qǐng)總線。主計(jì)算機(jī)需要讀取圖像數(shù)據(jù)時(shí),先給FPGA發(fā)送請(qǐng)求,然后FPGA收回EMIF的部線控制權(quán),PCI9054通過(guò)FPGA讀取SRAM中的圖像數(shù)據(jù)。圖5是系統(tǒng)進(jìn)入 正常跟蹤狀態(tài)時(shí)EMIF總線的占用時(shí)序圖。 每一場(chǎng)圖像處理的時(shí)序相同,其中: %26;#183;FPGA從FIFO中讀取圖像數(shù)據(jù),并存儲(chǔ)在SRAM中的時(shí)序?yàn)椋褐芷赥1=4.2ms,總線占用時(shí)間T2=0.3ms; %26;#183;DSP讀取處理窗中的圖像數(shù)據(jù)的時(shí)序?yàn)椋壕嚯x下一場(chǎng)圖像開始時(shí)間T3=7.95ms,總線占用時(shí)間T4=0.16ms; %26;#183;主機(jī)讀取圖像數(shù)據(jù)的時(shí)序?yàn)椋褐芷赥5=20ms,總線占用時(shí)間T6=2.3ms。 TMS320C6202的擴(kuò)展總線上掛接的設(shè)備除了DSP外,還有PCI9054和邏輯控制電路。TMS320C6202的擴(kuò)展總線的連接情況請(qǐng)參照?qǐng)D6。TMS320C6202內(nèi)部的擴(kuò)展總線仲裁器被禁用。擴(kuò)展總線的缺省占用設(shè)備是邏輯控制電路。PIC9054要占用擴(kuò)展總線就必須向邏輯控制電路申請(qǐng)總線占用權(quán)。 2.2.2 系統(tǒng)邏輯控制設(shè)計(jì) FPGA在系統(tǒng)啟動(dòng)時(shí)根據(jù)主機(jī)發(fā)送的命令對(duì)系統(tǒng)進(jìn)行自檢,其中有對(duì)A/D轉(zhuǎn)換器、FIFO等器件的復(fù)位操作;在系統(tǒng)進(jìn)入正常工作狀態(tài)時(shí),它還需要控制FLASH和SRAM的讀寫,并且通過(guò)設(shè)置寄存器,讓DSP和主機(jī)了解FIFO、SRAM、FLASH所處的狀態(tài),并使FPGA按要求將每幀圖像數(shù)據(jù)存放在SRAM內(nèi)的指定位置。

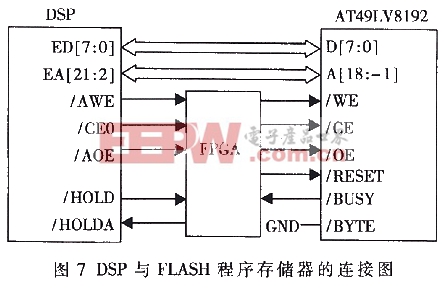

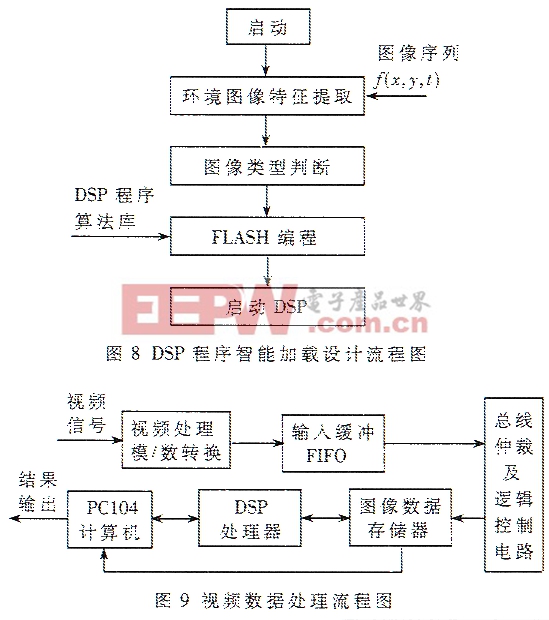

每一場(chǎng)圖像處理的時(shí)序相同,其中: %26;#183;FPGA從FIFO中讀取圖像數(shù)據(jù),并存儲(chǔ)在SRAM中的時(shí)序?yàn)椋褐芷赥1=4.2ms,總線占用時(shí)間T2=0.3ms; %26;#183;DSP讀取處理窗中的圖像數(shù)據(jù)的時(shí)序?yàn)椋壕嚯x下一場(chǎng)圖像開始時(shí)間T3=7.95ms,總線占用時(shí)間T4=0.16ms; %26;#183;主機(jī)讀取圖像數(shù)據(jù)的時(shí)序?yàn)椋褐芷赥5=20ms,總線占用時(shí)間T6=2.3ms。 TMS320C6202的擴(kuò)展總線上掛接的設(shè)備除了DSP外,還有PCI9054和邏輯控制電路。TMS320C6202的擴(kuò)展總線的連接情況請(qǐng)參照?qǐng)D6。TMS320C6202內(nèi)部的擴(kuò)展總線仲裁器被禁用。擴(kuò)展總線的缺省占用設(shè)備是邏輯控制電路。PIC9054要占用擴(kuò)展總線就必須向邏輯控制電路申請(qǐng)總線占用權(quán)。 2.2.2 系統(tǒng)邏輯控制設(shè)計(jì) FPGA在系統(tǒng)啟動(dòng)時(shí)根據(jù)主機(jī)發(fā)送的命令對(duì)系統(tǒng)進(jìn)行自檢,其中有對(duì)A/D轉(zhuǎn)換器、FIFO等器件的復(fù)位操作;在系統(tǒng)進(jìn)入正常工作狀態(tài)時(shí),它還需要控制FLASH和SRAM的讀寫,并且通過(guò)設(shè)置寄存器,讓DSP和主機(jī)了解FIFO、SRAM、FLASH所處的狀態(tài),并使FPGA按要求將每幀圖像數(shù)據(jù)存放在SRAM內(nèi)的指定位置。 當(dāng)FIFO處于半滿狀態(tài)時(shí),控制邏輯電路收回EMIF接口總線的占用權(quán)。獲得總線占用權(quán)后,開始讀取FIFO中的數(shù)據(jù),直到FIFO被讀空以后才釋放EMIF總線。在系統(tǒng)中,F(xiàn)IFO中的圖像數(shù)據(jù)是按8位存儲(chǔ)的,SRAM中的圖像數(shù)據(jù)是按32位來(lái)組織的,所以控制邏輯電路要把從FIFO中讀出的8位圖像數(shù)據(jù)裝配成32位數(shù)據(jù)后再寫到SRAM中。 2.3 DSP程序智能加載設(shè)計(jì) TMS320C6202有兩種存儲(chǔ)器映射方式:MAP0和MAP2。通過(guò)擴(kuò)展總線的XD[4:0]利用上拉/下拉電阻進(jìn)行復(fù)位時(shí)的芯片啟動(dòng)模式設(shè)置。系統(tǒng)中將存儲(chǔ)器映射方式設(shè)置為1,即地址0處的存儲(chǔ)器在內(nèi)部,芯片自加載方式為8bit ROM方式。圖7給出的是系統(tǒng)中設(shè)計(jì)的以一片F(xiàn)LASH(AT49LV8192)作為程序存儲(chǔ)器與DSP的連接圖。AT49LV8192的存儲(chǔ)空間為1Mbyte。 由于FPGA和DSP對(duì)FLASH的操作共享,因此要實(shí)現(xiàn)對(duì)FLASH的編程操作必須要通過(guò)這兩個(gè)設(shè)備。如果采用DSP采用編程,則需要先給DSP加載一個(gè)燒寫FLASH的程序,并且需要將燒寫的程序存儲(chǔ)在數(shù)據(jù)區(qū)內(nèi),這種方法復(fù)雜而且不容易實(shí)現(xiàn)。本系統(tǒng)采用的方法是:由主機(jī)通過(guò)FPGA對(duì)FLASH進(jìn)行編程。首先主機(jī)通知FPGA將要進(jìn)行編程,由FPGA收回EMIF總線,并告知主機(jī);接收主機(jī)將編程數(shù)據(jù)寫給FPGA,并由它負(fù)責(zé)對(duì)FLASH執(zhí)行寫操作。 在系統(tǒng)的運(yùn)行過(guò)程中,系統(tǒng)可以根據(jù)作戰(zhàn)環(huán)境不同以及操作指令的不同,自適應(yīng)地對(duì)DSP加載不同的程序,從而實(shí)現(xiàn)DSP程序動(dòng)態(tài)加載設(shè)計(jì),并增加系統(tǒng)的靈活性和智能化程序。其工作流程如圖8所示。 即系統(tǒng)在啟動(dòng)的時(shí)候,由主控計(jì)算機(jī)對(duì)當(dāng)前所處環(huán)境的圖像進(jìn)行特征提取,并加以分析、判斷,根據(jù)判斷結(jié)果從主控計(jì)算機(jī)的DSP程序算法庫(kù)中選出適合當(dāng)前環(huán)境特點(diǎn)的算法程序,來(lái)給圖像處理板上的FLASH芯片進(jìn)行編程,編程完畢后啟動(dòng)DSP的BOOTLOADER,將FLASH中的程序加載進(jìn)來(lái)。這樣就實(shí)現(xiàn)了DSP程序的自適應(yīng)加載功能。

當(dāng)FIFO處于半滿狀態(tài)時(shí),控制邏輯電路收回EMIF接口總線的占用權(quán)。獲得總線占用權(quán)后,開始讀取FIFO中的數(shù)據(jù),直到FIFO被讀空以后才釋放EMIF總線。在系統(tǒng)中,F(xiàn)IFO中的圖像數(shù)據(jù)是按8位存儲(chǔ)的,SRAM中的圖像數(shù)據(jù)是按32位來(lái)組織的,所以控制邏輯電路要把從FIFO中讀出的8位圖像數(shù)據(jù)裝配成32位數(shù)據(jù)后再寫到SRAM中。 2.3 DSP程序智能加載設(shè)計(jì) TMS320C6202有兩種存儲(chǔ)器映射方式:MAP0和MAP2。通過(guò)擴(kuò)展總線的XD[4:0]利用上拉/下拉電阻進(jìn)行復(fù)位時(shí)的芯片啟動(dòng)模式設(shè)置。系統(tǒng)中將存儲(chǔ)器映射方式設(shè)置為1,即地址0處的存儲(chǔ)器在內(nèi)部,芯片自加載方式為8bit ROM方式。圖7給出的是系統(tǒng)中設(shè)計(jì)的以一片F(xiàn)LASH(AT49LV8192)作為程序存儲(chǔ)器與DSP的連接圖。AT49LV8192的存儲(chǔ)空間為1Mbyte。 由于FPGA和DSP對(duì)FLASH的操作共享,因此要實(shí)現(xiàn)對(duì)FLASH的編程操作必須要通過(guò)這兩個(gè)設(shè)備。如果采用DSP采用編程,則需要先給DSP加載一個(gè)燒寫FLASH的程序,并且需要將燒寫的程序存儲(chǔ)在數(shù)據(jù)區(qū)內(nèi),這種方法復(fù)雜而且不容易實(shí)現(xiàn)。本系統(tǒng)采用的方法是:由主機(jī)通過(guò)FPGA對(duì)FLASH進(jìn)行編程。首先主機(jī)通知FPGA將要進(jìn)行編程,由FPGA收回EMIF總線,并告知主機(jī);接收主機(jī)將編程數(shù)據(jù)寫給FPGA,并由它負(fù)責(zé)對(duì)FLASH執(zhí)行寫操作。 在系統(tǒng)的運(yùn)行過(guò)程中,系統(tǒng)可以根據(jù)作戰(zhàn)環(huán)境不同以及操作指令的不同,自適應(yīng)地對(duì)DSP加載不同的程序,從而實(shí)現(xiàn)DSP程序動(dòng)態(tài)加載設(shè)計(jì),并增加系統(tǒng)的靈活性和智能化程序。其工作流程如圖8所示。 即系統(tǒng)在啟動(dòng)的時(shí)候,由主控計(jì)算機(jī)對(duì)當(dāng)前所處環(huán)境的圖像進(jìn)行特征提取,并加以分析、判斷,根據(jù)判斷結(jié)果從主控計(jì)算機(jī)的DSP程序算法庫(kù)中選出適合當(dāng)前環(huán)境特點(diǎn)的算法程序,來(lái)給圖像處理板上的FLASH芯片進(jìn)行編程,編程完畢后啟動(dòng)DSP的BOOTLOADER,將FLASH中的程序加載進(jìn)來(lái)。這樣就實(shí)現(xiàn)了DSP程序的自適應(yīng)加載功能。 2.4 視頻數(shù)據(jù)流分析 車載跟蹤系統(tǒng)的視頻數(shù)據(jù)處理流程如圖9所示。由該圖可以分析出現(xiàn)視頻數(shù)據(jù)的轉(zhuǎn)移流程: (1) 模擬視頻信號(hào)從攝像機(jī)進(jìn)入視頻接口模塊,由視頻接口電路采集、處理原始視頻信號(hào),得到統(tǒng)一的數(shù)字視頻數(shù)據(jù)和視頻同步信號(hào)。 (2) 數(shù)字視頻數(shù)據(jù)從視頻接口模塊進(jìn)入輸入緩沖FIFO,當(dāng)FIFO到達(dá)半滿狀態(tài)時(shí),由邏輯控制電路發(fā)出讀取FIFO數(shù)據(jù)的請(qǐng)求。邏輯控制電路收回EMIF接口總線的占用權(quán)后,由邏輯控制電路讀取FIFO中的數(shù)據(jù),寫入到SRAM中。在這個(gè)過(guò)程中,邏輯控制電路還要把四個(gè)8位的圖像數(shù)據(jù)裝配成32位的圖像數(shù)據(jù)。 (3) 當(dāng)邏輯控制電路向SRAM寫完一幀圖像數(shù)據(jù)時(shí),首先判斷DSP程序是否啟動(dòng),如果未啟動(dòng),則給PCI9054發(fā)出中斷,請(qǐng)求PC104計(jì)算機(jī)處理圖像數(shù)據(jù);;否則,向DSP發(fā)出圖像存放完成的中斷,請(qǐng)求DSP處理圖像數(shù)據(jù)。 (4) DSP開始從SRAM中讀取數(shù)據(jù),然后進(jìn)行處理,并將處理結(jié)果通過(guò)擴(kuò)展總線經(jīng)由邏輯控制電路和PIC9054送到PC機(jī)。 (5) PCI接口電路通過(guò)邏輯控制電路讀取SRAM中裝配好的視頻數(shù)據(jù),并由它送往PC機(jī),并結(jié)合DSP的處理結(jié)果,顯示處理后的視頻圖像和運(yùn)動(dòng)目標(biāo)的一些特征數(shù)據(jù)。 3 硬件平臺(tái)調(diào)試及性能測(cè)試 以TMS320C6202為核心器件設(shè)計(jì)的數(shù)字圖像跟蹤系統(tǒng)充分發(fā)揮了DSP的強(qiáng)大運(yùn)算能力和接口能力,在采用相應(yīng)的跟蹤算法時(shí),可在≤8ms的時(shí)間內(nèi)給出目標(biāo)參數(shù)。現(xiàn)以最費(fèi)時(shí)的模板圖像匹配算法對(duì)系統(tǒng)運(yùn)行時(shí)間進(jìn)行估計(jì)。

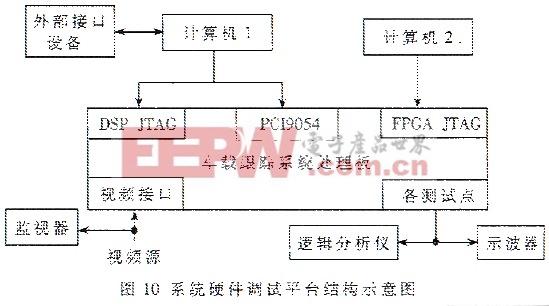

2.4 視頻數(shù)據(jù)流分析 車載跟蹤系統(tǒng)的視頻數(shù)據(jù)處理流程如圖9所示。由該圖可以分析出現(xiàn)視頻數(shù)據(jù)的轉(zhuǎn)移流程: (1) 模擬視頻信號(hào)從攝像機(jī)進(jìn)入視頻接口模塊,由視頻接口電路采集、處理原始視頻信號(hào),得到統(tǒng)一的數(shù)字視頻數(shù)據(jù)和視頻同步信號(hào)。 (2) 數(shù)字視頻數(shù)據(jù)從視頻接口模塊進(jìn)入輸入緩沖FIFO,當(dāng)FIFO到達(dá)半滿狀態(tài)時(shí),由邏輯控制電路發(fā)出讀取FIFO數(shù)據(jù)的請(qǐng)求。邏輯控制電路收回EMIF接口總線的占用權(quán)后,由邏輯控制電路讀取FIFO中的數(shù)據(jù),寫入到SRAM中。在這個(gè)過(guò)程中,邏輯控制電路還要把四個(gè)8位的圖像數(shù)據(jù)裝配成32位的圖像數(shù)據(jù)。 (3) 當(dāng)邏輯控制電路向SRAM寫完一幀圖像數(shù)據(jù)時(shí),首先判斷DSP程序是否啟動(dòng),如果未啟動(dòng),則給PCI9054發(fā)出中斷,請(qǐng)求PC104計(jì)算機(jī)處理圖像數(shù)據(jù);;否則,向DSP發(fā)出圖像存放完成的中斷,請(qǐng)求DSP處理圖像數(shù)據(jù)。 (4) DSP開始從SRAM中讀取數(shù)據(jù),然后進(jìn)行處理,并將處理結(jié)果通過(guò)擴(kuò)展總線經(jīng)由邏輯控制電路和PIC9054送到PC機(jī)。 (5) PCI接口電路通過(guò)邏輯控制電路讀取SRAM中裝配好的視頻數(shù)據(jù),并由它送往PC機(jī),并結(jié)合DSP的處理結(jié)果,顯示處理后的視頻圖像和運(yùn)動(dòng)目標(biāo)的一些特征數(shù)據(jù)。 3 硬件平臺(tái)調(diào)試及性能測(cè)試 以TMS320C6202為核心器件設(shè)計(jì)的數(shù)字圖像跟蹤系統(tǒng)充分發(fā)揮了DSP的強(qiáng)大運(yùn)算能力和接口能力,在采用相應(yīng)的跟蹤算法時(shí),可在≤8ms的時(shí)間內(nèi)給出目標(biāo)參數(shù)。現(xiàn)以最費(fèi)時(shí)的模板圖像匹配算法對(duì)系統(tǒng)運(yùn)行時(shí)間進(jìn)行估計(jì)。 設(shè)匹配模板為16%26;#215;16,匹配搜索范圍為48%26;#215;48,逐點(diǎn)匹配,以MAD準(zhǔn)則為匹配準(zhǔn)則,每個(gè)像素點(diǎn)的計(jì)算需要四條DSP指令,指令周期為4ns。則系統(tǒng)運(yùn)行結(jié)果為: 每次匹配運(yùn)算的像素個(gè)數(shù)為:16%26;#215;16; 搜索區(qū)內(nèi)匹配次數(shù)為:(48-16)%26;#215;(48-16)=32%26;#215;32; 總匹配運(yùn)算時(shí)間為:16%26;#215;16%26;#215;32%26;#215;32%26;#215;4%26;#215;4ns≈4.19ms。 可以看出,系統(tǒng)的運(yùn)算能力滿足系統(tǒng)處理圖像數(shù)據(jù)的需求。 整個(gè)系統(tǒng)的調(diào)試工作可以分為硬件調(diào)試、軟件調(diào)試、軟硬件硬調(diào)三個(gè)部分。硬件系統(tǒng)的調(diào)試從總體上看可分為兩個(gè)部分:硬件系統(tǒng)的基本測(cè)試和各個(gè)功能模塊的調(diào)試。圖10給出的是硬件系統(tǒng)的調(diào)試平臺(tái)。 在調(diào)試過(guò)程中,硬件系統(tǒng)的功能調(diào)試可劃分為以下幾個(gè)部分:視頻接口、輸入緩沖FIFO的讀寫操行、DSP程序存儲(chǔ)器FLASH的讀寫操作、圖像幀存儲(chǔ)器的讀寫操作、DSP與PCI9054的HPI接口、主計(jì)算機(jī)和PCI9054的讀寫操作等調(diào)試。通過(guò)編寫相關(guān)的調(diào)試程序可驗(yàn)證硬件電路的正確性。 基于DSP的智能圖像跟蹤系統(tǒng)在繼承成熟技術(shù)的基礎(chǔ)上,運(yùn)用先進(jìn)的圖像處理和模式識(shí)別技術(shù),采用高速DSP處理器、雙CPU并行處理的模式,確保了系統(tǒng)運(yùn)行可靠、跟蹤精度高,具有很好的抗干擾、抗復(fù)雜背景的能力。將圖像跟蹤系統(tǒng)應(yīng)用在裝甲戰(zhàn)車上,使其和戰(zhàn)車指揮系統(tǒng)整合為一個(gè)完整的數(shù)字式系統(tǒng),將是裝甲戰(zhàn)車發(fā)展一個(gè)必然趨勢(shì)。可以預(yù)見,此系統(tǒng)的研制成功及在裝甲車輛上的廣泛應(yīng)用,將大大推動(dòng)裝甲車輛的技術(shù)進(jìn)步。

設(shè)匹配模板為16%26;#215;16,匹配搜索范圍為48%26;#215;48,逐點(diǎn)匹配,以MAD準(zhǔn)則為匹配準(zhǔn)則,每個(gè)像素點(diǎn)的計(jì)算需要四條DSP指令,指令周期為4ns。則系統(tǒng)運(yùn)行結(jié)果為: 每次匹配運(yùn)算的像素個(gè)數(shù)為:16%26;#215;16; 搜索區(qū)內(nèi)匹配次數(shù)為:(48-16)%26;#215;(48-16)=32%26;#215;32; 總匹配運(yùn)算時(shí)間為:16%26;#215;16%26;#215;32%26;#215;32%26;#215;4%26;#215;4ns≈4.19ms。 可以看出,系統(tǒng)的運(yùn)算能力滿足系統(tǒng)處理圖像數(shù)據(jù)的需求。 整個(gè)系統(tǒng)的調(diào)試工作可以分為硬件調(diào)試、軟件調(diào)試、軟硬件硬調(diào)三個(gè)部分。硬件系統(tǒng)的調(diào)試從總體上看可分為兩個(gè)部分:硬件系統(tǒng)的基本測(cè)試和各個(gè)功能模塊的調(diào)試。圖10給出的是硬件系統(tǒng)的調(diào)試平臺(tái)。 在調(diào)試過(guò)程中,硬件系統(tǒng)的功能調(diào)試可劃分為以下幾個(gè)部分:視頻接口、輸入緩沖FIFO的讀寫操行、DSP程序存儲(chǔ)器FLASH的讀寫操作、圖像幀存儲(chǔ)器的讀寫操作、DSP與PCI9054的HPI接口、主計(jì)算機(jī)和PCI9054的讀寫操作等調(diào)試。通過(guò)編寫相關(guān)的調(diào)試程序可驗(yàn)證硬件電路的正確性。 基于DSP的智能圖像跟蹤系統(tǒng)在繼承成熟技術(shù)的基礎(chǔ)上,運(yùn)用先進(jìn)的圖像處理和模式識(shí)別技術(shù),采用高速DSP處理器、雙CPU并行處理的模式,確保了系統(tǒng)運(yùn)行可靠、跟蹤精度高,具有很好的抗干擾、抗復(fù)雜背景的能力。將圖像跟蹤系統(tǒng)應(yīng)用在裝甲戰(zhàn)車上,使其和戰(zhàn)車指揮系統(tǒng)整合為一個(gè)完整的數(shù)字式系統(tǒng),將是裝甲戰(zhàn)車發(fā)展一個(gè)必然趨勢(shì)。可以預(yù)見,此系統(tǒng)的研制成功及在裝甲車輛上的廣泛應(yīng)用,將大大推動(dòng)裝甲車輛的技術(shù)進(jìn)步。

評(píng)論