免費的I/O:改進FPGA時鐘分配控制

本文引用地址:http://www.104case.com/article/241684.htm

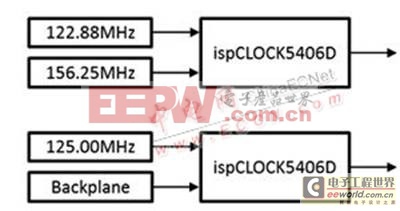

本文引用地址:http://www.104case.com/article/241684.htm圖4 AMC時鐘網(wǎng)絡(luò)控制

可編程性重新定義了時鐘網(wǎng)絡(luò)

一個可編程的時鐘分配IC,如ispClock5406D專門為高性能的通信和計算應(yīng)用而設(shè)計,如PCI Express、ATCA、MicroTCA和AMC。這些可編程IC的主要功能包括一個超低相位噪聲的PLL、輸出部分支持多種邏輯標準和雙偏移控制。

這類可編程時鐘分配IC的主要優(yōu)點包括:

可編程偏移通過減少蜿蜒的走線從而簡化了電路板布局,并有助于增加時序容限、縮短設(shè)計時間。

能夠通過一個可編程的輸出阻抗特性來匹配走線阻抗。與更高的輸出VCC和接地引腳相結(jié)合,提高了時鐘信號的完整性。此外,由于輸出阻抗可以按每個器件來調(diào)整,器件與器件間輸出阻抗的差異最小化,從而提高生產(chǎn)合格率。一個片上可編程輸出阻抗還可以彌補使用輸出阻抗匹配電阻而引起的要用更大的電路板面積的需求。

一個通用扇出緩沖器,可以通過編程來驅(qū)動多種信號標準,減少了對獨立的(有時部分使用)信號轉(zhuǎn)換器的需求,因此減少了時鐘網(wǎng)絡(luò)的層次,并且降低了整個電路板的時序要求。

低抖動和良好匹配的輸出-輸出偏移,可以提供額外的時序容限。

每個IC的配置可保存在片上非易失性存儲器中,通過JTAG接口進行重新編程。然后器件的某些特定方面可以通過一個I2C接口進行修改。因為該器件的所有的主要功能都是可編程的,設(shè)計人員可以使用標準化的器件,如ispClock5406D以滿足其系統(tǒng)時鐘需求,并且降低成本。

綜述

可編程時鐘器件集成了主要的時序元件,如一個PLL、分頻器、扇出緩沖器、零延遲緩沖器,從而節(jié)省電路板面積、降低成本,并提高性能。使用諸如ispClock5400D系列器件,設(shè)計人員可以更好地規(guī)劃其特定系統(tǒng)的理想時鐘產(chǎn)生和分配電路,更好地利用其FPGA上的I/O。

評論