以可編程方式打造加密引擎

我們的系統基于Missing Link Electronics(MLE)公司的“軟”硬件平臺,其FPGA具有靈活的I/O,能夠連接各種傳感器和執行器。該平臺采用可編程邏輯實現片上系統,以MicroBlaze CPU或PowerPC CPU作為其核心。CPU為操作系統與用戶空間應用軟件運行MLE Linux軟件棧。由于采用MicroBlaze或PowerPC作為主CPU,當運行嵌入式Linux操作系統外加強大加密功能時,該系統顯然無法提供所需要的計算性能,而且也無法改變物理硬件。為了實現系統加速,我們使用可編程系統將計算從軟件域轉移到硬件側。

協處理硬件

可編程系統基本上是一個或幾個CPU(運行操作系統與應用軟件)的組合,外加一個FPGA。FPGA在其中用作靈活的接口“適配器”以及協處理硬件。我們可以在單獨輔助芯片上實現可編程系統,或者將全部都集成到單個器件上。我們可以根據FPGA器件和CPU之間的通信方式,采用不同方法調節系統性能和功能。

其中一種方法就是添加對等處理器,通過內存映射狀態和控制寄存器與CPU實現同步。因為通過同一系統總線運行所有通信會很快降低性能,因此我們希望把CPU數據流與對等處理器分開。而采用賽靈思的Central DMA或多端口儲存器控制器(MPMC)等片上系統組件能夠輕松滿足上述愿望。

另外,也可以增加一個協處理器,這種情況下能通過增加自定義指令(也叫編譯功能)有效地擴展CPU的指令集。例如,它適合浮點單元,而且賽靈思的結構協處理器模塊(FCM)技術能輕松支持上述功能。此處的優勢是在CPU和協處理器之間使用一條從內存到系統總線的專用通信通道。對于PowerPC,其為輔助處理單元(APU),而對于MicroBlaze,則是快速單工鏈路(FSL)。

在加密和解密中,大部分運算按行或列執行,剩下四項運算并行計算,硬件對此任務得心應手。

AES:黃金標準

但是沒有重大的系統重新設計,又該如何真正加速加密?對于加密,高級加密標準(AES)是一個事實標準。

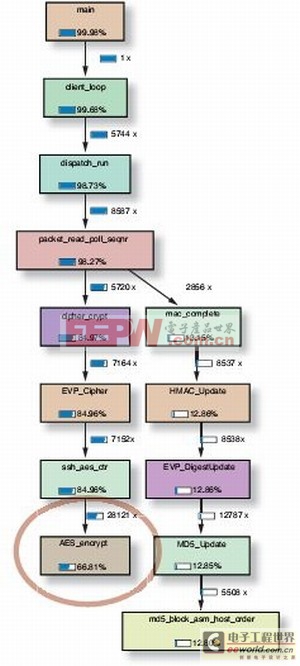

采用AES加密時,無法通過定義減少計算任務,從而使嵌入式系統很快達到性能極限。如圖1所示,其中顯示用Valgrind分析工具、通過SCP(SSH會話)進行的文件傳輸的分析結果。此時AES加密占用三分之二計算任務。

圖1:在采用Valgrind工具的SCP傳輸中,AES加密占用三分之二的計算任務。

AES-128采用密鑰和128位塊大小,使用許多并發8字節運算。AES屬于分組密碼,基于按4x4字節陣列組織的固定分組大小運算。我們曾經采用128位分組大小,它能抵擋所有已知攻擊,安全性甚至強于192位和256位版本。

采用128位AES時,執行加密與解密需要12個回合,每個回合需要幾步運算。第一項任務是通過所謂的密鑰擴展過程從密鑰中算出回合金鑰。每個回合都采用純文本自身的回合密鑰執行純文本的逐位異或運算。然后進行字節代替、行位移和列混合運算,并再次執行回合金鑰的異或運算。

最后一個回合稍有不同,因為其中省略了一些步驟。加密過程采用所謂的S盒(其提供非線性)執行替代。我們可以把它安置到一個16?16?8位矩陣中,從而能夠適應常見的賽靈思BRAM原語。多個S盒實例可以加速IP核,并在適當的位置為內核提供所需數據,而無需等待對主存儲器的長時間總線存取。解密過程大同小異,其采用相同密鑰,但方向相反,并且使用不同S盒。

增速12倍

在加密和解密中,大部分運算按行或列執行,剩下四項運算并行計算—而硬件對此任務得心應手。這樣就能夠通過不同來源實現AES硬件的各個部分。為了加速系統,我們從龐大、快速增長的OpenCores.org資源庫(http://opencores.org/project,avs_aes)獲取AES內核。

我們刪除了原有的總線接口(因為它適用于另一種FPGA架構),另外為APU添加了一個接口,以便把AES內核作為FCM協處理器連接到PowerPC上。我們共使用8個所謂的UDI指令在PowerPC和AESFCM之間傳輸數據。

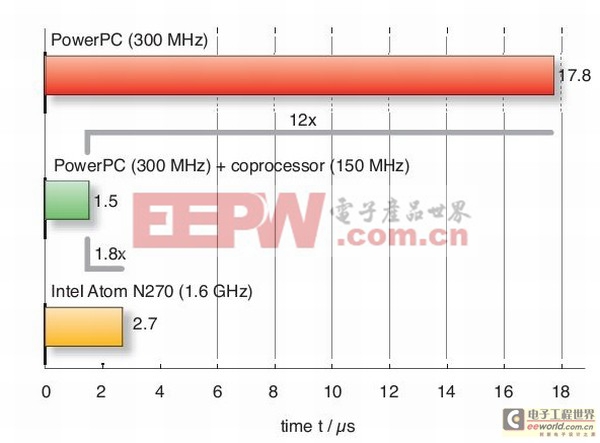

工作結果非常令人滿意(見圖2)。硬件加速的系統比原實現方案快了12倍。原來用以300MHz運行的獨立的PowerPC加密一個單塊需要17.8微秒,而采用以150MHz運行的AESFCM只需1.5微秒。如果只以升級到速度稍快的CPU來加速運算,我們采用硬件加速后的1.5微秒速度表現超過基于Intel Atom1.6GHz CPU的純軟件實現(其需要2.7微秒)。上述結果證明了使用FPGA技術的硬件加速的卓越潛能。

圖2:硬件加速系統(中間綠條)快于獨立的PowerPC或Atom處理器。

評論