一種基于FPGA的可配置SPI Master接口設計實現

隨著現場可編程門陣列(FPGA)芯片在商業、軍事、航空航天等領域的廣泛應用,其可靠性和可測試性顯得尤為重要。對設計人員來說,FPGA的使用相當靈活。然而,正是這種應用的不確定性和重復可編程性,增加了芯片的測試難度。其核心問題是建立什么樣的測試模型才能使故障激活。根據需求,FPGA的測試大體可分為面向制造的測試過程(MTP)和面向應用的測試過程(ATP)兩類。MTP主要是從制造商的角度來測試,ATP是在應用級上的測試,也就是把FPCA配置為特定的功能進行測試,具有很強的針對性。本文介紹ATP測試中SPI Master模型的建立。在測試FPGA設計的集成電路時,對設計電路的性能進行實時測試是必不可少的環節。這就需要設計一種接口電路,將測試數據送人設計電路。

1 SPI總線協議介紹

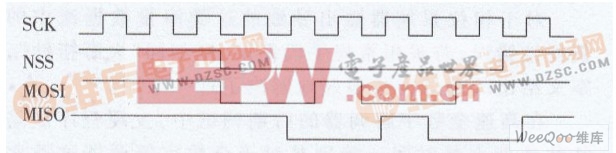

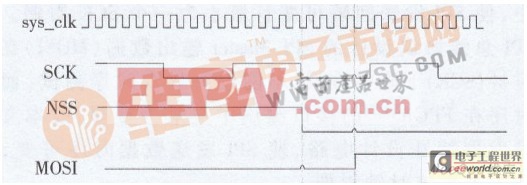

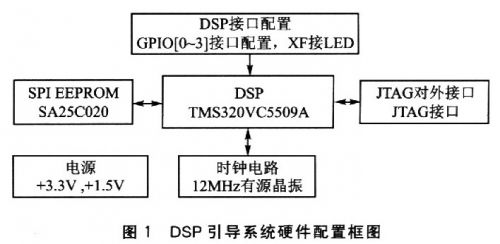

SPI(Seri。n Perpheral Interface)是一種高速的、全雙工、同步的通信總線,并且在芯片的管腳上只占用4根線,節約了芯片的管腳,同時為PCB的布局節省空間,提供方便,正是出于這種簡單易用的特性,越來越多的芯片集成了這種通信協議。SPI的通信原理很簡單,它以主從方式工作,這種模式通常有一個主設各和一個或多個從設備,需要至少4根線,事實上3根也可以(用于單向傳輸時,也就是半雙工方式)。也是所有基于SPI的設各共有,分別是MIS0(數據輸人),M0SI(數據輸出),SCK(時鐘),NSS(片選),如圖1所示。

圖1 SPI總線時

(1)M0SI:主設備數據輸出,從設備數據輸人。

(2)MISO:主設各數據輸人,從設備數據輸出。

(3)SCK:時鐘信號,由主設各產生。

(4)NSS:從設各使能信號,由主設各控制。

使能信號低電平有效,當使能信號為低電平時,輸出數據(M0SI)在串行時鐘(SCK)下降沿變化,輸人數據(MIS0)在(SCK)上升沿變化。

2 SPI Master原理

本文介紹的基于FPGA的、可配置的SPI Master接口設計,能滿足測試的各種正常、異常以及強度測試要求。此SPI接口模塊可設置為單次發送、循環發送(發送間隔可設);發送數據長度可變;串行時鐘線(SCK)與輸出數據線(MOSI)時序關系可變;串行時鐘線(SCK)與使能信號(NSS)時序關系可變。

一般情況下,為了SPI數據發送的靈活性,SPI發送次數及發送間隔是由軟件實現的,當需要循環發送且發送間隔達到微秒甚至納秒數量級時,軟件很難實現。本文將SPI發送次數以及發送間隔集成到SΠ Master模塊中,使SPI發送間隔可變且最小為一個SCK周期。按照SPI總線協議設計的SPI Master輸出數據(M0SI)在串行時鐘(SCK)下降沿變化,不能進行異常時序測試,而異常時序在FPGAH的接口測試中又最為重要,故本文利用觸發器特性設計電路,使SPI發送數據時序可變,精度為1個系統時鐘周期。

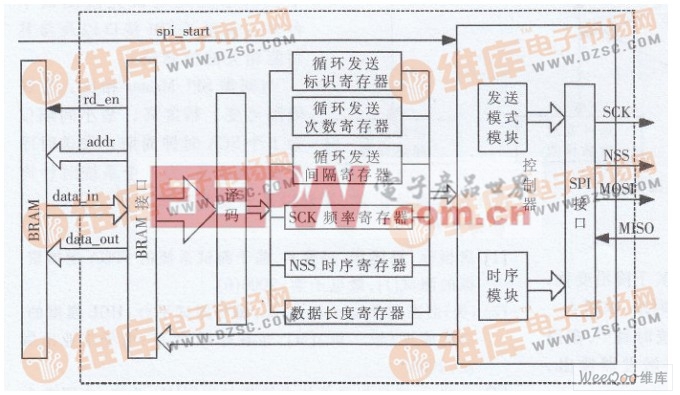

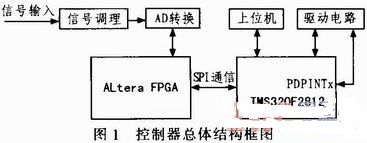

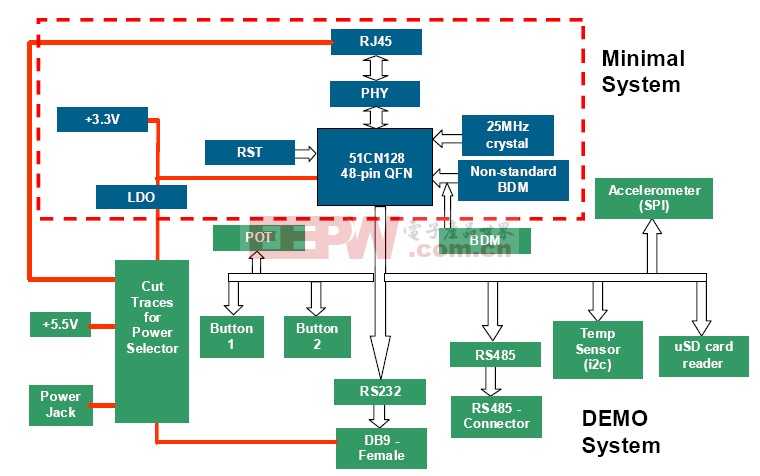

3 SP丨Master模塊結構圖

SPI Master模塊由Bram接口、配置寄存器、控制器三部分組成,如圖2所示。此模塊系統時鐘為100 MHz。

圖2 SPI Master模塊結構圖

BRAY接口:控制配置參數以及SPI數據的讀寫配置參數及SPI數據在BRAM中存儲結構如表1所示。

表1 BRAM存儲結構表

控制器:解析配置寄存器,產生發送時序,控制BRAM接口進行數據讀寫。

對配置寄存器說明如下。

(1)循環發送標識寄存器:1 bit,高電平標識循環發送,低電平標識單次發送。

{2)循環發送次數寄存器:15 bit,若循環發送標識為高電平時,此寄存器值為要發送的數據長度,單位:B;發送模塊中包含一發送次數計數器,NSS從高電平變為低電平,發送次數計數器加1。

(3)循環發送間隔寄存器:16 bit,若循環發送標識為高電平時,此寄存器值為每兩次發送間隔,單位:10 ns。(最小間隔為1個SCK周期,若小于1個SCK周期,則從設各不能檢測到NSS信號變化),發送模塊中包含1個發送間隔計數器,從一次SPI發送結束開始計數,直到與循環發送間隔寄存器中值相等,啟動下次發送。

(4)SCK頻率寄存器:16 bit,此寄存器值表示串行時鐘tCK周期,單位為10 ns(系統時鐘為100 MHz,精度為⒛ns);時序模塊中包含一分頻模塊,SCK周期=(SCK頻率寄存器)×10 ns。

(5)M0SI時序寄存器:8 bit,此寄存器值表示M0SI變化與SCK下降沿間隔時間,單位:10 ns(系統時鐘為100 MHz,因此最小間隔為lO ns)。

(6)數據長度寄存器:16 bit,此寄存器值表示要發送數據的長度,單位:B。

(7)NSS時序寄存器:8 bit,此寄存器值表示NSS變化與SCK下降沿間隔時間,單位:lO ns(系統時鐘為100 MHz,因此最小間隔為lO ns)。

4 SPI Master模塊功能介紹

(1)SPI循環發送次數可變,范圍:1~32 767;(2)SPI數據發送長度可變,范圍:1~65 535,單位:B;(3)SPI循環發送間隔可變,范圍:(1個SCK周期)~(65 536×10 ns),實現了連續發送,即一次SPI發送結束后下一SCK時鐘立即啟動下次SPI發送;(4)MOSI與SCK時序關系可變,NSS與SCK時序關系可變,SPI總線為下降沿發送,上升沿接收,故MOSI、NSS在SCK下降沿后半個周期可調即可。

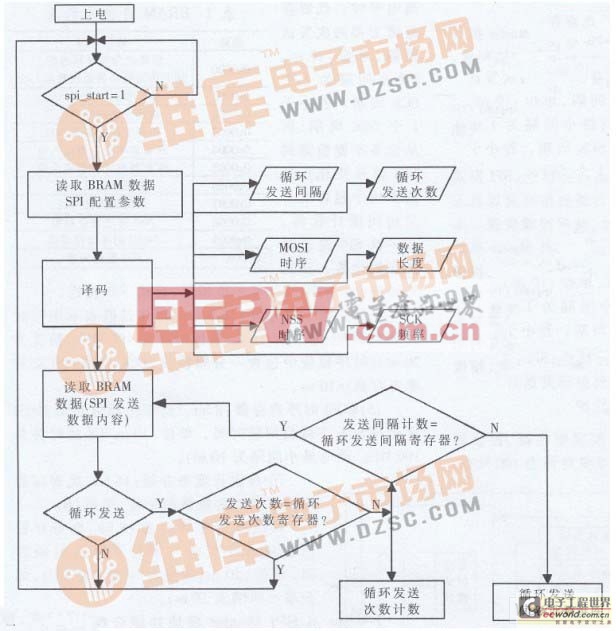

SPI功能流程如圖3所示,FPGA上電復位后不斷檢測SPI start信號,當SPI stalt信號有效時(高電平)啟動SPI發送,讀取BRAM中的配置參數,進行澤碼,依據譯碼后數據長度值讀取BRAM中數據,按照SPI協議發送數據;完成一次SPI發送后判斷是否為循環發送,若為循環發送則啟動下一次SPI發送,直到發送次數等于循環發送次數寄存器值,萁中發送間隔由循環發送間隔寄存器值決定。

圖3功能流程圖

4.1單次發送(正常時序)

SPI Master控制器檢測到SPl_start信號有效,即控制Bram接口讀取配置參數,經譯碼后若循環發送標識寄存器為低電平,則配合發送長度寄存器讀取BRAM中數據,并進行發送。

4.2單次發送(異常時序)

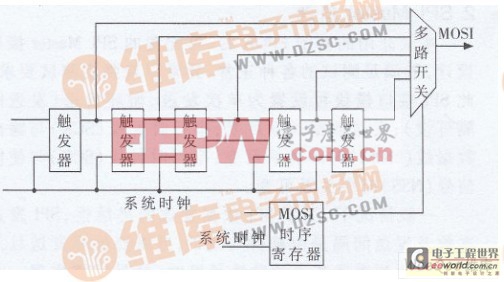

M051異常時序:正常情況下M0SI在SCK下降沿變化,此設計采用一帶抽頭的序列寄存器產生異常時序,如圖4。

圖4異常時序產生模塊結構圖

每增加一個觸發器,延時增加一個系統時鐘,多路開關依據M051日寸序寄存器中值選擇相應觸發器輸出,產生異常時序,舉例說明如圖5。

圖5中sys_clk為系統時鐘頻率100 MHz,NSS為使能信號;MOSI為串行輸出信號;當SCK頻率寄存器為10時,SPI串行時鐘SCK周期=(SCK頻率寄存器)×10 ns=100 ns,即SCK頻率為10 MHz;當M0SI時序寄存器值為4時,M0SI在SCK下降沿后4個sys elk開始變化。

圖5 SPI異常時序圖

4.3循環發送(時序正常)

每完成一次SPI發送,發送次數計數器加1,當發送次數計數器中的值與循環發送次數寄存器中值相等時,完成循環發送。發送次數由循環發送次數寄存器值決定,循環發送間隔由發送間隔計數器決定。

4.4循環發送(時序異常)

類似循環發送(正常時序),異常時序產生類似單次發送(異常時序)。

實現的目標器件是Xilinx的Vitex2 pro開發板。本文已應用于中國科學院光電研究院測試平臺中,實現了SPI接口以及與其功能相關的的測試。與同類SPI Master相比,發送間隔可變、精度高,最小間隔僅為1個SCK時鐘周期;發送時序可變,精度高,為1個系統時鐘周期;基本滿足正常、異常以及強度等測試要求。

評論