嵌入式1394總線接口的設(shè)計(jì)和實(shí)現(xiàn)

一、 引言

IEEE1394 是1986 年由蘋果電腦公司針對(duì)高速數(shù)據(jù)傳輸開發(fā)的一種總線接口,并于1995年由美國電氣和電子工程師協(xié)會(huì)(IEEE)制定成標(biāo)準(zhǔn),旨在取代并行SCSI 接口。目前為止,它主要發(fā)展為IEEE1394-1995,1394a,1394b 等系列標(biāo)準(zhǔn)。1394 作為一個(gè)工業(yè)標(biāo)準(zhǔn)的高速串行總線,已經(jīng)被廣泛應(yīng)用于數(shù)字?jǐn)z像機(jī)、數(shù)字照相機(jī)、電視機(jī)頂盒、計(jì)算機(jī)及其外圍設(shè)備、DVD 設(shè)備等等,甚至在航天軍事領(lǐng)域也有一定的應(yīng)用潛力。這些設(shè)備便攜性的需求加快了它們集成度的提高,這些都將使1394 總線與嵌入式處理器的結(jié)合有很廣闊的應(yīng)用前景。

等時(shí)傳輸模式的優(yōu)越性使1394 總線廣泛應(yīng)用于圖像傳輸領(lǐng)域,而數(shù)字信號(hào)處理器(DSP)在圖像等信號(hào)處理方面具有很大優(yōu)勢(shì),因此基于DSP 實(shí)現(xiàn)的1394 總線接口在圖像傳輸和處理領(lǐng)域有著廣泛的應(yīng)用需求,但是,DSP 芯片與1394 總線芯片時(shí)序一般不能直接匹配。本文提出了一種基于DSP 的1394 總線接口實(shí)現(xiàn)方案,能在基于DSP 處理器的嵌入式系統(tǒng)上方便地實(shí)現(xiàn)1394 總線接口,具有較強(qiáng)的現(xiàn)實(shí)意義。

二、 設(shè)計(jì)方案

1394 總線協(xié)議包括物理層,鏈路層,傳輸層,應(yīng)用層以及串行總線管理器。目前已經(jīng)有很多廠家能提供1394 總線接口的協(xié)議芯片,可以很容易地實(shí)現(xiàn)1394 總線接口本身。本文主要介紹如何通過FPGA 實(shí)現(xiàn)嵌入式處理器與1394 總線鏈路層控制器芯片的匹配,嵌入式處理器把1394 總線設(shè)備作為外設(shè)實(shí)現(xiàn)數(shù)據(jù)讀取和寫入。整體結(jié)構(gòu)框圖如圖1。其中DSP 是本文使用的嵌入式處理器類型,1394 鏈路層控制器和1394 物理層控制器是1394 總線協(xié)議芯片。FPGA 是現(xiàn)場可編程門陣列,是本文用于實(shí)現(xiàn)DSP 與1394 鏈路層控制器匹配的主要芯片,與分立器件相比,它具有可擦除、功耗小、體積小和調(diào)試方便等優(yōu)勢(shì)。本文選用ACTEL 公司生產(chǎn)的APA300 芯片來完成設(shè)計(jì),它有30 萬門陣列資源,已經(jīng)遠(yuǎn)遠(yuǎn)滿足本設(shè)計(jì)的需求。

2.1 TMS320V33

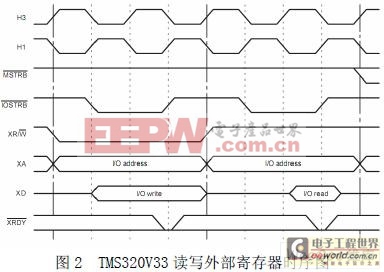

德州儀器(TI)在DSP 設(shè)計(jì)廠商中具有領(lǐng)先優(yōu)勢(shì),TMS320V33 是TI 推出的TMS320 系列的第三代處理器的升級(jí)版本的32 位浮點(diǎn)運(yùn)算數(shù)字信號(hào)處理器,也是目前國內(nèi)外使用最為廣泛的浮點(diǎn)DSP 芯片之一。它有24 位地址總線和32 位數(shù)據(jù)總線,本設(shè)計(jì)中使用高17 位地址信號(hào)作為選通信號(hào),低7 位地址信號(hào)作為輸出給鏈路層芯片的有效地址信號(hào),低16 位數(shù)據(jù)總線作為有效數(shù)據(jù)信號(hào),H1 是37.5Mhz 時(shí)鐘信號(hào)。TMS320V33 讀寫外部寄存器時(shí)序如圖2。

2.2 鏈路層控制器

目前能提供 1394a 鏈路層控制器芯片的廠商有很多,芯片種類也很多。而其中TI 公司生產(chǎn)的TSB12LV32 功能全面,應(yīng)用廣泛。它是一款高性能通用1394a 鏈路層控制器,它主要實(shí)現(xiàn)1394 鏈路層協(xié)議。圖3 和圖4 是1394 鏈路層芯片TSB12LV32 的握手模式讀寫時(shí)序圖。其中BCLK 代表時(shí)鐘信號(hào)輸入,最大工作頻率是60Mhz;MWR 代表讀寫使能信號(hào)輸入,高電平時(shí)讀使能有效,低電平時(shí)寫使能有效;MCS 代表選通信號(hào)輸入,低電平有效;MCA 代表選通應(yīng)答信號(hào)輸出,低電平有效;MA 代表地址信號(hào)輸入;MD 代表雙向數(shù)據(jù)信號(hào);另外COLDFIRE,M8BIT/SIZ0,MCMODE/SIZ1 為設(shè)置工作模式專用信號(hào)。在本設(shè)計(jì)中我們選用握手工作模式。

2.3 方案選擇

鏈路層控制器最高僅 60Mhz 的理論工作頻率使得高性能的TMS320V33 必須增加自己的讀寫周期才能與之很好的配合,TMS320V33 的讀寫周期可以通過RDY 信號(hào)或者增加可編程等待狀態(tài)改變。在本設(shè)計(jì)中我們對(duì)TMS320V33 使用RDY 信號(hào)的方法來配合它與鏈路層芯片的讀寫時(shí)序。兩種方法沒有好壞之分,區(qū)別僅在于DSP 可編程等待狀態(tài)的數(shù)量是有限的,但是大部分情況下增加有限的等待狀態(tài)已經(jīng)足夠。

我們可以選擇使用組合邏輯和時(shí)序邏輯來完成此FPGA 設(shè)計(jì),雖然組合邏輯設(shè)計(jì)方法簡單、占用資源少,但是它僅僅是讓DSP 和鏈路層芯片的讀寫時(shí)序“湊”到一起,很難實(shí)現(xiàn)完全配合,而且會(huì)在讀寫過程中存在很多“毛刺”、“競爭”和“冒險(xiǎn)”,不適合應(yīng)用在性能要求比較高的場合。有限狀態(tài)機(jī)是時(shí)序邏輯的一種,它由狀態(tài)、狀態(tài)轉(zhuǎn)換條件和狀態(tài)輸出組成。它具有以下優(yōu)點(diǎn):1.它是同步時(shí)序電路,克服了組合邏輯順序控制不靈活的缺點(diǎn),便于與CPU 配合;2.狀態(tài)機(jī)容易構(gòu)成性能良好的同步時(shí)序邏輯模塊,只需要將“毛刺”控制在下一個(gè)狀態(tài)到來之前,這對(duì)于對(duì)付設(shè)計(jì)中的“競爭冒險(xiǎn)”現(xiàn)象無疑是一個(gè)較好的辦法;3.狀態(tài)機(jī)的結(jié)構(gòu)模式相對(duì)簡單,設(shè)計(jì)方案相對(duì)固定,設(shè)計(jì)方法具有通用性。

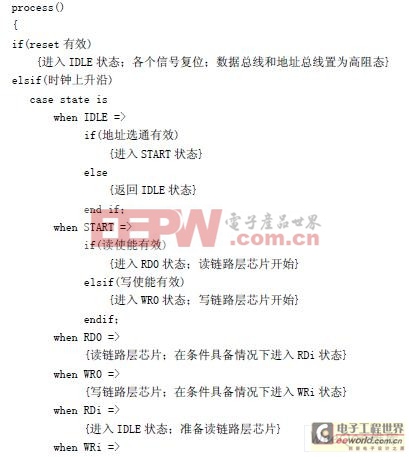

基于以上情況,本設(shè)計(jì)中使用“有限狀態(tài)機(jī)”的方法實(shí)現(xiàn)嵌入式處理器與鏈路層芯片的時(shí)序匹配,保證在處理器的一次讀寫操作中數(shù)據(jù)能正確有效地傳送。結(jié)合圖2、圖3 和圖4的讀寫時(shí)序給出狀態(tài)轉(zhuǎn)換圖如圖5。此狀態(tài)機(jī)一共由6 個(gè)狀態(tài)組成,分別為IDLE、START、RD0、RDi、WR0、WRi。在RESET 信號(hào)有效時(shí)設(shè)計(jì)進(jìn)入復(fù)位階段,復(fù)位后狀態(tài)機(jī)進(jìn)入IDLE 狀態(tài);在IDLE 狀態(tài)中,如果片選信號(hào)有效,狀態(tài)機(jī)進(jìn)入START 狀態(tài),同時(shí)輸出給鏈路層控制器MCS 端口低信號(hào),選通鏈路層芯片寄存器;狀態(tài)機(jī)進(jìn)入START 狀態(tài)后,開始檢測讀寫使能信號(hào),如果讀(寫)信號(hào)有效,則進(jìn)入RD0(WR0)狀態(tài),同時(shí)向鏈路層控制器芯片讀(寫)的地址;在RD0(WR0)狀態(tài)中,檢測鏈路層控制器芯片的MCA 管腳信號(hào),在MCA 有效時(shí)讀(寫)有效數(shù)據(jù),并向DSP 輸出RDY 有效信號(hào),狀態(tài)機(jī)進(jìn)入RDi(WRi)狀態(tài),經(jīng)過一個(gè)時(shí)鐘后釋放數(shù)據(jù)和地址總線,返回IDLE 狀態(tài)。

三、 設(shè)計(jì)實(shí)現(xiàn)

目前用于 FPGA 設(shè)計(jì)的主流硬件描述語言主要有VHDL 和verilog HDL,本設(shè)計(jì)借助VHDL語言實(shí)現(xiàn)。下面簡要列出實(shí)現(xiàn)狀態(tài)機(jī)的VHDL 代碼結(jié)構(gòu):

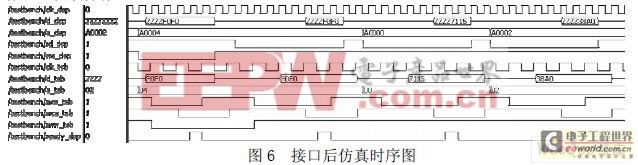

將此設(shè)計(jì)方法實(shí)現(xiàn)的電路下載到實(shí)際系統(tǒng)中進(jìn)行驗(yàn)證,試驗(yàn)結(jié)果表明,該設(shè)計(jì)能成功完成TMS320V33 對(duì)TSB12LV32 芯片讀寫控制功能。接口后仿真時(shí)序如圖6 所示,包括一次寫操作和三次讀操作。

四、 結(jié)論

本設(shè)計(jì)實(shí)現(xiàn)的 TMS320V33 與1394 總線鏈路層芯片TSB12LV32 的接口設(shè)計(jì)方法,設(shè)計(jì)思路清晰,時(shí)序準(zhǔn)確,并且具有一定的靈活性和通用性,其他類似處理器與1394 總線鏈路層芯片的接口都可以采用類似的設(shè)計(jì)方法。

本文的設(shè)計(jì)方法為其它各種處理器與外設(shè)接口的匹配設(shè)計(jì)實(shí)現(xiàn)提供了有益的參考。

linux操作系統(tǒng)文章專題:linux操作系統(tǒng)詳解(linux不再難懂) 電機(jī)保護(hù)器相關(guān)文章:電機(jī)保護(hù)器原理

評(píng)論