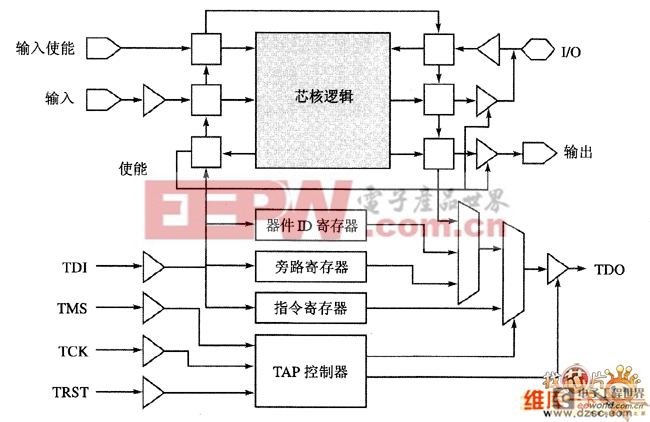

JTAG接口的結(jié)構(gòu)組成

圖1 JTAG調(diào)試接口示意圖

(1)TAP(測(cè)試訪問(wèn)端口)控制器

TAP控制器對(duì)嵌入在ARM處理器核內(nèi)部的測(cè)試功能電路的訪問(wèn)控制,是一個(gè)同步狀態(tài)機(jī),通過(guò)測(cè)試模式選擇TMS和時(shí)鐘信號(hào)TCK來(lái)控制其狀態(tài)機(jī)。通過(guò)測(cè)試模式選擇TMS和時(shí)鐘信號(hào)TCK *控制其狀態(tài)轉(zhuǎn)移,實(shí)現(xiàn)IEEE1149.1標(biāo)準(zhǔn)所確定的測(cè)試邏輯電路的工作時(shí)序。

(2)指令寄存器

指令寄存器是串行移位寄存器,通過(guò)它可以串行輸入執(zhí)行各種操作的指令。

(3)數(shù)據(jù)寄存器組

數(shù)據(jù)寄存器組是一組串行移位寄存器。操作指令被串行裝入由當(dāng)前指令所選擇的數(shù)據(jù)寄存器,隨著操作的進(jìn)行,測(cè)試結(jié)果被串行移出。其中:

·器件ID寄存器:讀出在芯片內(nèi)固化的D號(hào)。

·旁路寄存器:1位移位寄存器,用一個(gè)時(shí)鐘的延遲把TDI連接至TDO,使測(cè)試者在同一電路板測(cè)試循環(huán)內(nèi)訪問(wèn)其他器件。

·邊界掃描寄存器(掃描鏈):截取ARM處理器核與芯片引腳之間的所有信號(hào),組成專用的寄存器位。

評(píng)論