基于ISA總線的高速同步數據采集系統設計

CPU1主要用于數據采集、與PC機通訊;CPU2用于接收GPS時間報文,GPS時間報文可在任何時刻由CPU1從與之相接的雙口RAM2中讀取。高速雙端口RAM IDT7130(2K×8位)、IDT7134(4K×8位),內部具有判決電路以防止因對某一單元同時操作而產生沖突。雙口RAM1IDT7134主要用于CPU1存放采集的數據、同步時間信息及工作狀態等,供PC機定時取用,同時也接收來自PC機的命令。雙口RAM2 IDT7130其容量為2K字節,主要用于CPU1與CPU2交換GPS的同步時鐘信息。

對高速數據采集技術而言,最為重要的是系統的分辨率、精度與通過速率。特別是系統通過速率,是區別高速數據采集與一般數據采集最為關鍵的一項技術指標。在硬件的具體實現過程中,則需要考慮兩個方面:(1)A/D轉換器的轉換時間;(2)轉換后的數據存儲時間[2]。

1.1 高速A/D轉換

A/D轉換采用閃爍ADC器件AD9048,其最大轉換速率為35MSPS,分辨率為8位。利用高速雙極工藝制造,采樣速率快,頻帶寬,無代碼遺失,輸入電容小(僅為16pF),功耗低(為500mW)。AD9048內部時鐘鎖定比較器可使編碼邏輯電路和輸出緩沖寄存器作在35MSPS的高速,并避免了多數系統對取樣保持電路(S/H)和跟蹤保持電路(T/H)的需要。數字輸入、輸出及控制電平與TTL兼容。AD589和AD741、2N3906等構成穩壓可調電路,提供給9048的RB、RT接地。AD9618作為輸入緩沖放大器[3]。由于AD9048的數據輸出沒有三態門控制,故在輸出加上74LS241作三態門控制。AD9048是否工作取決于輸入轉換脈沖信號,在脈沖信號上升沿取樣。轉換脈沖來自采樣頻率控制電路中的8254分頻器的輸出。

1.2 高速尋址

對于高速數據采集系統,A/D轉換應不受CPU控制。每當ADC轉換一次后,由控制電路發出相應的信號,將ADC轉換結果寫入高速緩存RAM某單元中,再使地址計數器加1,直到地址計數器記滿后產生采樣結束信號,封鎖RAM寫信號,利用二進制地址發生器的最高位通過中斷方式通知主機采樣已完成。

地址計數器可根據地址位數由若干同步記有選舉權器級聯而成,五片74LS163可構成19位地址形成電路。計數器每收到一個脈沖即產生一個地址。地址的初值可通過時序控制電路清零。若采用循環地址,則在計數滿后,用進位信號迫使計數器的同步預置電平發生變化,使計數器恢復初值,進入新一輪計數。

1.3 快速存儲

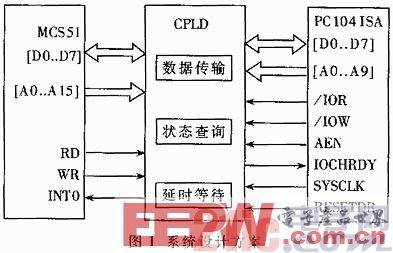

單片機與上位PC機間串口通訊的數據傳輸速率往往不能滿足實時要求;DMA通道最的大數據傳輸率也不超過5MB/s[1],這顯然無法滿足本系統中高達20MB/s的采樣速度。為了解決高速數據采集與低速數據傳輸的矛盾,在單片機系統中,數據存儲器選用雙端口RAM IDT7134(圖1中RAM1)。在上位PC主機與單片機之間建立了一個4K字節大小的緩沖區,單片機只須將經過預處理的采樣值通過一個端口存放緩沖區,上位PC主機通過另一端口從緩沖區取數據。這樣就解決了高速采樣與低速數據傳輸的矛盾,可滿足實時采集和控制的要求。

評論