交換接口控制器的可擴展設(shè)計

與傳統(tǒng)ASIC相比,F(xiàn)PGA和結(jié)構(gòu)化ASIC的優(yōu)勢在于重用靈活性高、上市時間快、性能佳而成本低。FPGA和專用的IP模塊可用于現(xiàn)有的商用AdvancedTCA平臺,可用來開發(fā)可擴展的交換接口控制器(FIC),以加快產(chǎn)品開發(fā)的設(shè)計并使線卡方案具有魯棒性和成本效益。

當今通信和計算系統(tǒng)制造商正在基于模塊化系統(tǒng)架構(gòu)設(shè)計下一代平臺,以縮短開發(fā)周期、降低新設(shè)備的資本開支,并在增加新功能和服務時最大限度地減少運營費用。模塊化平臺使設(shè)備制造商能夠在一套通用的構(gòu)建模塊上設(shè)計多種類型的系統(tǒng),從而通過實現(xiàn)一定的規(guī)模經(jīng)濟效應保持競爭力。

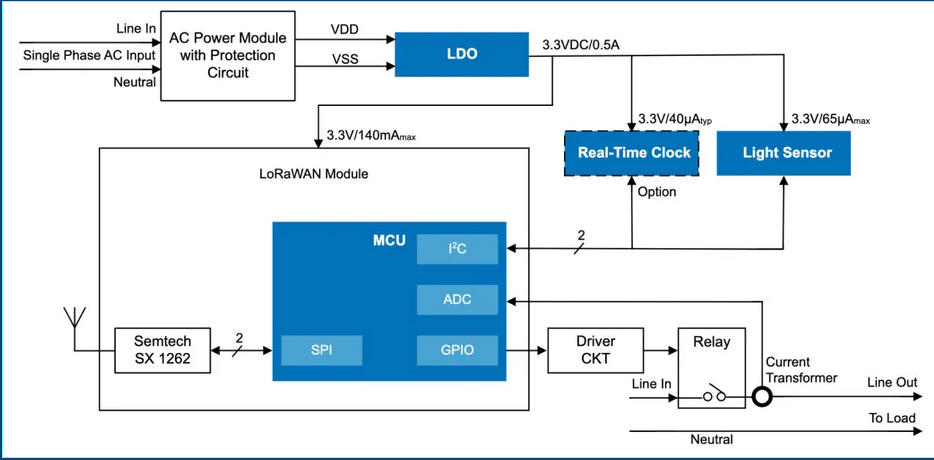

圖1:一個SPI4.2到ASI交換接口控制器的功能圖。左邊是SPI4.2到NPU的接口,右邊是ASI到交換結(jié)構(gòu)的連接。

實現(xiàn)模塊化的必不可少的一步是使設(shè)備制造商共同創(chuàng)建一組用于電路板和機架的通用物理互連標準。AdvancedTCA就是由PCI工業(yè)計算機制造商組織(PICMG)定義的一種系統(tǒng)構(gòu)造參數(shù),它為諸如機架尺寸、線卡、I/O模塊、交換接口(星狀和網(wǎng)狀結(jié)構(gòu)拓撲)、額定功率等等平臺單元提供了標準規(guī)范。AdvancedTCA標準的主要目標是提供一個基于標準的硬件平臺,這個硬件平臺由機架和存儲刀片、網(wǎng)絡(luò)處理器卡、控制平面刀片,以及管理模塊的組合來構(gòu)建模塊化運營級產(chǎn)品,這些產(chǎn)品針對電信接入?yún)R聚平臺和邊緣平臺應用。

AdvancedTCA背板接口的工業(yè)標準集的定義,使系統(tǒng)集成商在他們的交換接口卡和線卡之間互連具有更大的靈活性和互操作性。AdvancedTCA網(wǎng)絡(luò)接口采用開放的接口協(xié)議,并采用子規(guī)范PICMG 3.1-3.5提供可互操作的電路板。這些子規(guī)范支持以太網(wǎng)、光纖通道、Infiniband、PCI Express、STarFabric、高級交換互連(ASI)和串行RapidIO。一些大型OEM向AdvancedTCA規(guī)范的轉(zhuǎn)移標志著從定制、專有的和基于互連的平臺向基于開放標準的COTS平臺轉(zhuǎn)移。

PCI Express和ASI

系統(tǒng)可擴展性和模塊化需要通用互連以支持多種應用中芯片和/或子系統(tǒng)的無縫集成。隨著背板性能從40Gbps提升到160甚至320Gbps,必須仔細設(shè)計以確保交換結(jié)構(gòu)和數(shù)據(jù)流源頭之間的接口不會出現(xiàn)傳輸瓶頸。交換接口必須在支持關(guān)鍵的結(jié)構(gòu)需求,諸如數(shù)據(jù)吞吐、流控制和按流排隊的同時,以良好的信號完整性高效地傳輸2.5Gbps到超過10Gbps的數(shù)據(jù)流。

|

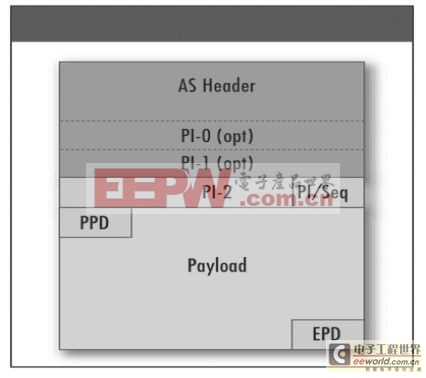

圖2:包含ASI報頭、可選的PI0和PI1報頭及一個PI2報頭的TLP。 |

PCI Express和ASI是兩種標準的交換結(jié)構(gòu)技術(shù),它們有潛力使標準、最新的交換設(shè)備和交換接口器件的市場急劇增長。PCI Express具有跨越從計算到通信生態(tài)系統(tǒng)的制造、技術(shù)支持和產(chǎn)品開發(fā)的經(jīng)濟規(guī)模。把PCI Express移植到串行互連的好處在于:具有物理和性能上的可擴展性;改善了可靠性;實現(xiàn)了全雙工傳輸;布線和電纜連接更簡單、成本更低。

ASI通過定義兼容的擴展來增強PCI Express,從而解決諸如對等通信的支持、QoS、多播和支持多協(xié)議封裝的要求。PCI Express和ASI是互補協(xié)議,許多系統(tǒng)兩者都采用以滿足目前尚無法實現(xiàn)的設(shè)計要求。隨著新型組幀器、網(wǎng)絡(luò)處理單元(NPU)和交換結(jié)構(gòu)采用ASI,有必要將ASI與其它接口規(guī)范橋接起來,例如與SPI3、SPI4.2和CSIX橋接。這種橋接功能可以方便地與交換接口控制器集成在一起。

FIC架構(gòu):

一個SPI4.2到ASI控制器的功能(圖1)包括:

1. ASI到SPI4.2的雙向橋接,可從2.5Gbps擴展到20Gbps(x1、x4或x8路);

2. 為端點和橋接組裝和分拆ASI事務層數(shù)據(jù)包(TLP);

3. 支持1到64,000個連接隊列(CQ);

4. 在SPI4.2上支持多達16個通道;

5. 可編程通道映射到SPI4.2;

6. 支持一個可旁路的、三個有序的和一個多播虛擬通道(VC);

7. 可編程最大數(shù)據(jù)包長度為64到80字節(jié);

8. 鏈路層基于信用量的流控制;

|

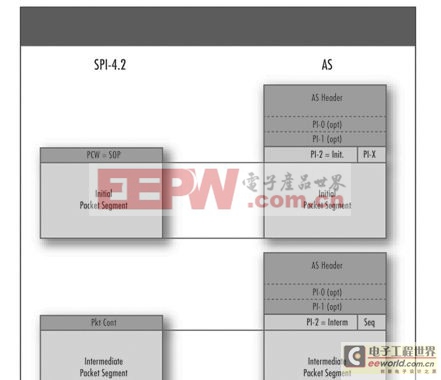

圖3:PI2封裝示例。通過去除SPI4.2協(xié)議控制字(PCW)并增加ASI報頭、可選PI0和PI1報頭以及PI2報頭,初始SPI4.2突發(fā)數(shù)據(jù)流被轉(zhuǎn)換到ASI TLP之中。 |

9. CRC生成和誤碼校驗;

10. 處理連續(xù)的背靠背數(shù)據(jù)包結(jié)束符(EOP);

11. DIP4奇偶位生成和校驗;

12. 狀態(tài)通道組幀、DIP2生成和校驗;

13. 狀態(tài)同步生成丟失和檢測;

14. 訓練序列生成和檢測;

15. 全同步設(shè)計(800Mbps);

16. 與OIF兼容的SPI4階段2;

17. 與ASI-SIG兼容,ASI核心架構(gòu)規(guī)范修訂版1.0。

在SPI4.2到ASI方向,必要時對進入的SPI4.2數(shù)據(jù)包進行分段,并根據(jù)流量類型(單播或多播)和等級映射到VC FIFO緩沖器。用戶在SPI4到VC映射表中對緩沖到SPI4.2接口的通道映射信息進行編程,接口上的數(shù)據(jù)包按照表中所示傳輸?shù)较鄳木彌_器。ASI調(diào)度器讀取隊列并將TLP發(fā)送到交換結(jié)構(gòu)。

每一個SPI4.2通道FIFO緩沖器的填充水平被轉(zhuǎn)換為“空虛-未滿-飽滿”狀態(tài),并通過接收狀態(tài)通道(RSTAT)發(fā)送到對等的SPI4.2發(fā)送器。當有空間時,在SPI4.2接口上接收的數(shù)據(jù)包被傳輸?shù)较鄳腣C FIFO緩沖器。

SPI4.2和每一個VC支持最多16個通道(通道0到15)。下面是從SPI4.2到VC的示范通道分配:

1. SPI4.2通道0到7被映射為8個可旁路虛擬通道(BVC);

2. SPI4.2通道8到11被映射為4個有序虛擬通道(OVC);

3. SPI4.2通道12到15被映射為4個多播虛擬通道(MVC)。

ASI到SPI4.2的輸出數(shù)據(jù)包流

在ASI到SPI4.2方向,采用可編程地址映射表(圖2),從指定VC的交換結(jié)構(gòu)輸出的ASI TLP和流量等級被映射到16個SPI4.2通道中的一個。用戶在VC到SPI4表中對VC到SPI4.2接口的通道映射信息進行編程。數(shù)據(jù)復用(MUX)記錄表RAM(VCS4記錄表RAM)包含從VC接口FIFO緩沖器讀數(shù)據(jù)到把數(shù)據(jù)傳送至SPI4.2接口的調(diào)度。VCS4記錄表RAM有16個位置。

評論