基于CPLD非多路復用/多路總線轉換橋設計/實現

2 非多路復用總線的信號和時序

2.1 TMS320F206接口的主要信號說明

TMS320F206的總線接口方式采用地址和數據分離的形式。其主要信號有地址信號A0~A15、數據信號D0~D15、讀信號RE、寫信號WE、閘門信號STRB、I/O空間選擇信號IS、數據存儲器選擇信號DS、程序存儲器選擇信號PS、機器時鐘輸出信號CLKOUT1。當對外部數據存儲器、程序存儲器或I/O空間訪問時,STRB有效;當對外部I/O訪問時(即程序中使用PORTR和PORTW指令),IS有效。

2.2 TSM320F206的I/O時序分析

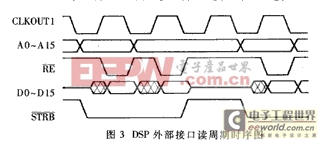

TMS320F206的讀寫時序如圖3和圖4所示。I/O的讀或寫工作周期一般在兩個機器周期內完成。在此期間,IS信號和地址信號一直保持有效;閘門信號STRB發生在第一個機器周期有效后并保持一個機器周期以上;RE和WE有效時,數據有效。兩次連續的寫操作(如圖4所示)時,WE的有效間隔時間tW(WH)最小為(2H-4)ns,而兩次連續的讀操作(如圖3所示)時,RE的有效間隔時間tW(RDH)為(H-4)ns~Hns,其中H為0.5倍的機器時鐘周期。可見對于連續的讀、寫操作,RE、WE的有效間隔不同,設計電路時應注意此細節。在連續的讀或寫操作時,IS信號一直為有效電平'0',無法以此信號作為產生SJA1000的ALE、讀、寫信號起始基準;而在寫周期時,STRB與WE的變化始終保持一致,因此在產生SJA1000寫周期時,可以用STRB作為ALE、WR產生的起始基準信號。但是TSM320F206在連續的讀操作時,STRB一直保持為低電平,可見在產生SJA1000讀、寫操作周期時,無法單獨以它作為ALE、RD信號產生的起始基準,需與IS、WE、RE進行邏輯組合來作為SJA1000讀、寫操作周期的起始基準信號。

|

|

3 CPLD實現轉換橋的設計方法

此轉換橋如果用中規模集成電路(74系列)實現起來比較復雜,工作頻率又較高,布線時若稍不合理,易引起干擾,使得電路工作不穩定,因此這里采用高可靠性的復雜可編程邏輯器件CPLD,用硬件描述語言VHDL來實現。

3.1 轉換橋引腳信號定義

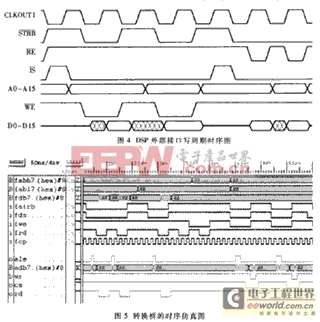

圖5為轉換橋的時序仿真圖,其中轉換橋的各引腳信號與TMS320F206和SJA1000lSJA10001引腳信號的對應為:fabl7接A0~A7;fdb7接D0~D7;fds接IS;fstrb接STRB;fwe接WE;frd接RE;fcp接CLKOUT1;ale接ALE;adb7接AD7~AD0;wr接WR;rd接RD。

3.2 SJA1000讀、寫周期使能信號和起始基準信號的確定

轉換橋的基準時鐘fcp為TMS320F206TMS320F206的機器時鐘輸出信號CLKOUT1。fcp為20MHz的方波信號。因為TMS320F206的讀或寫工作周期一般為一、兩個機器時鐘周期,此時基準時鐘fcp最多含有四個邊沿狀態,無法完成非多路復用到多路復用的轉換,所以通過軟件等待設置,使TMS320F206對外部總線操作時,由原來所用的一個機器時鐘周期延長到四個機器時鐘周期,邊沿狀態個數增加了4倍。另外fcp的脈寬為25ns,這樣可以保證轉換橋輸出的多路復用總線時序的時間參數滿足SJA1000的時序要求。從上面的時序分析中可以確定出SJA1000的讀、寫周期的使能信號(IS)和起始基準信號(STRB、WE、RE邏輯組合)。IS作為轉換橋的片選信號,當IS?quot;0"時,轉換橋工作;否則,轉換橋的各輸出信號被懸掛。當IS為"0"、STRB為"0"、WE為"0"、RE為"1"時,DSP開始對外部I/O進行寫操作,在后面緊跟的四個DSP機器時鐘周期產生出1個SJA1000的寫周期;當IS為"0"、STRB為"0"、WE為"1"、RE為"1"時,DSP開始對外部I/O進行讀操作,在后面緊跟的四個DSP機器時鐘周期產生出1個SJA1000的讀周期。

3.3 讀操作轉換過程

通過軟件等待設置,使DSP的 I/O讀、寫操作需四個機器時鐘周期。在第一個時鐘周期的上升沿產生ale信號(脈寬為0.5倍的機器時鐘周期),同時將DSP輸入的低八位地址fabl7鎖存并送到地址數據復用總線adb7,并保持到第二個時鐘周期的上升沿為止,此時adb7為高阻狀態。第三、第四個時鐘周期,DSP的讀信號frd有效,將此信號直接送到rd引腳,此時adb7引腳的數據直接送給fdb7引腳,讀操作結束。

3.4 寫操作轉換過程

在寫操作的四個時鐘周期中,在第一個時鐘周期的上升沿產生ale信號(脈寬為一個機器時鐘周期),同時將DSP輸入的低八位地址fabl7引腳的信號送到adb7上,并保持到第三個時鐘周期結束。在第四個時鐘周期的上升沿產生寫信號wr(寬度為一個時鐘周期),在DSP寫信號few的上升沿處鎖存數據線fdb7來的信號,并將其送到adb7引腳上,延時到第五個時鐘周期時把adb7變為高阻狀態,寫操作結束。

本文提出的非多路復用總線到多路復用總線轉換橋采用了Xilinx公司的CPLD芯片XC95144-15-PQ100,并使用該公司開發的集成環境Fundation F3.1i,將其集成為一塊專用芯片。通過大量的實驗測試,此轉換橋工作非常穩定,現已應用到電力網絡饋線遠程終端裝置(FTU)中。

評論