嵌入式流媒體攜帶式系統(tǒng)的設(shè)計及改進

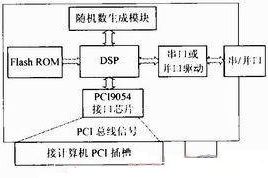

3.2 PCI接口設(shè)計

在該流媒體系統(tǒng)設(shè)計過程中所使用的PXA270處理器本身并不支持PCI總線協(xié)議,為了使系統(tǒng)能夠支持PCI總線協(xié)議,需要對處理器的接口進行改進,在這里提出使用FPGA來設(shè)計PCI總線接口控制器。設(shè)計在ModelSim環(huán)境下對Verilog HDL源程序進行前仿真,在Xilinx ISE環(huán)境下進行邏輯綜合、布局布線后下載到Xilinx公司生產(chǎn)Spartan-3 FPGA XC3S200芯片內(nèi)。GEC2410開發(fā)板套件

PCI接口控制器的設(shè)計中,核心設(shè)計部分有時序控制和配置空間兩部分。時序控制保證了PCI接口控制器能按正常的PCI時序工作。配置空間部分保證了板卡的即插即用功能。

3.2.1 PCI接口配置空間的實現(xiàn)

PCI總線定義了3種物理地址空間,分別是存儲器地址空間、I/O地址空間和配置地址空間。配置空間是PCI所特有的一種空間,其長度為256字節(jié)并且有特定記錄結(jié)構(gòu)的地址空間,可以在系統(tǒng)自舉時訪問,也可在其他時間訪問[3]。其它一些寄存器配置如下:GEC2410開發(fā)板套件

廠商ID使用芯片最初的生產(chǎn)廠商ID值;設(shè)備ID可為除00000000H和0FFFFFFFFH中的任意值;命令寄存器中位1、6、8在本設(shè)計中均被設(shè)置為0;基地址寄存器用來映射設(shè)備的存儲器地址空間,與設(shè)備地址空間大小相應(yīng)的低位被強制為0,故此在配置寫過程中,配置軟件通過對這個寄存器的所有位寫1,然后再讀出該寄存器的值來決定設(shè)備存儲器所占用的地址范圍,位0被設(shè)為低表示存儲器映射;類代碼寄存器:設(shè)置為018000H,即設(shè)備為大容量存儲控制器;首部類型寄存器:設(shè)置為0,表示其為單功能設(shè)備且首部類型為0。

3.2.2 時序控制的實現(xiàn)

在時序控制程序中采用狀態(tài)機模型來實現(xiàn)不同時序的轉(zhuǎn)換。各種命令,數(shù)據(jù)交換、控制均在狀態(tài)機的管理下進行工作。PCI總線上的信號是并行工作的,因此,對應(yīng)每個狀態(tài)必須明確其執(zhí)行的任務(wù),這些任務(wù)用Verilog語言的進程語句來描述所發(fā)生的事件。GEC2410開發(fā)板套件

本設(shè)計中的狀態(tài)機共使用了6種狀態(tài),如圖3所示,分別為空閑狀態(tài)(idle),準備狀態(tài)(Ready),DEVSEL# 和TRDY#均為高電平狀態(tài)(DevTrHi),DEVSEL#為低電平且TRDY#為高電平狀態(tài)(DevLoTrHi),DEVSEL#和TRDY#均為低電平狀態(tài)(DevTrLo)以及操作結(jié)束狀態(tài)(OprOver)。

圖3 PCI接口狀態(tài)機

注: state0表示pci_frame_i= ’1’ and pci_irdy_i =’1’, state 1表示pci_frame_i= ’1’ and pci_irdy_i=’0’ and irdy_i=’0’。

當系統(tǒng)接到復(fù)位信號后對系統(tǒng)進行復(fù)位,然后轉(zhuǎn)入空閑狀態(tài)。在空閑狀態(tài)中采樣總線,并根據(jù)總線的變化來決定下一個時鐘上升沿后狀態(tài)機轉(zhuǎn)人何種狀態(tài),這些時序和程序中用到的信號都是基本且必須的,在進行開發(fā)時可以根據(jù)需要增添必要的狀態(tài)和信號。編寫完整的代碼,之后將代碼導(dǎo)入ModelSim完成仿真,用Xilinx公司自帶工具ISE進行綜合布線,生成bit文件下載到FPGA器件。GEC2410開發(fā)板套件

4 系統(tǒng)的軟件模塊設(shè)計

該流媒體攜帶式系統(tǒng)的軟件平臺采用小體積、高性能的嵌入式Linux操作系統(tǒng),它由一個內(nèi)核和一些可以定制的系統(tǒng)模塊組成,如文件系統(tǒng)模塊、內(nèi)存驅(qū)動模塊等[5]。針對本應(yīng)用,進行了重新剪裁和配置,只包含系統(tǒng)所需的模塊。

對于該攜帶式系統(tǒng)的播放終端,其軟件應(yīng)用程序結(jié)構(gòu)如圖4所示,分別是圖形用戶界面模塊、系統(tǒng)管理主控模塊和音視頻解碼器三部分。音視頻解碼器模塊可看作是系統(tǒng)管理主控模塊的插件(plug-in),從主控模塊獲得編碼的音視頻數(shù)據(jù)并對其解碼,解碼后返發(fā)送給系統(tǒng)管理主控模塊。本文主要介紹系統(tǒng)管理主控模塊。

圖4 播放終端應(yīng)用程序結(jié)構(gòu)圖

評論