便攜式產(chǎn)品的低功耗電路系統(tǒng)的綜合考慮

此外,在系統(tǒng)設(shè)計中,粗略評估速度,并在可能的情況下適當改變元件的選擇,也可以降低功率。

下列方案可供選擇:

1. 降低工作電壓。當電壓從5V降低為3V時功耗將減少60%。

2. 采用智能電源。在系統(tǒng)中增加適當?shù)闹悄茴A(yù)測、檢測,并僅在需要時才對系統(tǒng)供電。許多膝上型電腦及其電源管理就具有這種特殊的機制,只給需要工作的電路加電,并在不必要時降低時鐘速率。

3. 采用較低的時鐘速率。由于CMOS電路中功率是開關(guān)頻率的函數(shù),因此較低的時鐘速率下器件的功耗也較小。

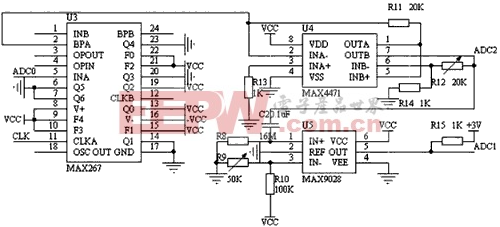

4. 對輸入信號作出限制。在模擬電路(包括A/D轉(zhuǎn)換器)中,限制輸入信號的帶寬有助于減少對高速電路的要求,如果有可能降低A/D轉(zhuǎn)換器的速率,也能減少功耗。

5. 對I/O進行設(shè)置,使它只在工作時消耗功率。但從不工作狀態(tài)到工作狀態(tài)的轉(zhuǎn)換需要較長的時間,另外一個副作用是可能產(chǎn)生與輸出電路有關(guān)的額外漏電流,使輸出電壓降至電源的一半,并使其它輸出電路處于很高的漏電交叉工作區(qū)域。

6. 擴大輸出范圍。對于許多ASIC來說,設(shè)計輸出電路僅用于驅(qū)動一個標準IC。通過重新調(diào)整電路使其足以驅(qū)動封裝和板上的寄生元件,并留出風扇負載的安全余量,這樣可以減小輸出電路尺寸和功率。

7. 改用其它技術(shù)。BiCMOS電路綜合了CMOS器件和雙極性器件的優(yōu)點,它是工藝復(fù)雜性更高以及成本更高的最佳折衷方案。GaAs器件也能滿足較低功耗和較高速度的要求,適用于那些以速度為主要設(shè)計目標的高價系統(tǒng)。

半導(dǎo)體制造商正在開發(fā)新的設(shè)計技術(shù)以滿足特殊功率要求,同時仍保證電路的性能指標要求。摩托羅拉半導(dǎo)體公司應(yīng)用工程師Pivot說,最終的目標是電路工作電壓小于1V,最后的極限值將取決于決定器件最小尺寸的器件工藝水平。低功率電路仍是人們需要深入調(diào)查研究的對象,在提高性能的同時降低功耗將是他們努力實現(xiàn)的目標。

系統(tǒng)設(shè)計者必須具備在有限的功率指標下實現(xiàn)更高電路性能的能力,另外還要滿足基本的系統(tǒng)性能指標要求、成本目標和上市時間要求。不過,設(shè)計者仍需要仔細分析系統(tǒng)中所有部件的功率情況。用于優(yōu)化功耗設(shè)計的新工具和新技術(shù)有助于改善設(shè)計環(huán)境,并使設(shè)計者的工作更加輕松。

評論