基于LpLVDS和CTL技術的便攜系統/O設計

I/O解決方案

如上所述,低功耗、高吞吐量以及超低電磁干擾信令技術是便攜和消費產品應用設計的關鍵。因此,類似LVDS的差分信令技術在改善數據吞吐能力、抗噪聲能力或電磁干擾性能方面成為系統的一個重要設計環節。LVDS的最大優點之一是其在正和負輸出端的電流方向相反。如果輸出正負端靠得夠近,應該能夠使電磁輻射相互抵消,這將大幅降低手機的電磁干擾和對手機本身通訊信號的影響。在手機等電池供電應用要求更低功耗的情況下,具有較低VCC工作能力的降低功耗LVDS技術版本(LpLVDS)是滿足便攜設計需求的關鍵。除了LpLVDS,飛兆半導體還開發了下一代I/O技術,即電流傳送邏輯(CTL),以提供更低功耗和更低電磁干擾的優勢。

圖1所示為各種接口信號技術的簡要比較以及CTL技術在1Gbps速度下的眼圖。與傳統LVDS技術相比,CTL技術每個通道的功耗要小30%。同時,CTLI/O的電磁干擾比傳統LVDS技術低10dB,比TTL技術低20dB。使用圖1中的波形圖可以解釋原因,對于相同的時間間隔(這意味著相同的吞吐量),CTL技術可以使用低很多的邊沿上升速率輕易地在邏輯“0”和“1”之間進行切換,而CTL的擺幅僅為65mV,較傳統LVDS技術的350mV量級相比小得多。較低的di/dt無疑能有效地減小磁性輻射。

數據傳送解決方案

LpLVDS和CTL只提供針對LCD、相機成像器以及基帶處理器之間接口的I/O解決方案。只有在采用某些并行至串行數據傳送方案時,兩者才能發揮其強大功能。借著鎖相環路(PLL)技術,可以利用PLL輸出的倍頻頻率將多個并行輸入轉換成串行流,這種電路一般稱為串化器。使用同樣的方式,當數據抵達顯示屏一側時,串行流經內部第二個PLL解碼,并被變換回并行TTL信號以驅動LCD模塊(LCM)。解碼電路被稱作解串器,傳統的串化器和解串器的雙PLL結構會增加功耗,飛兆半導體公司的單PLLuSerDes可以幫助設計人員借助LpLVDS和CTLI/O進一步節省功率,降低功耗。

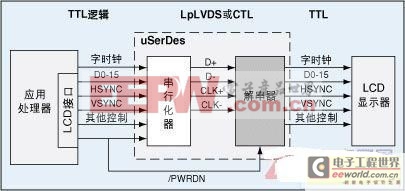

圖2:uSerDes在帶有RGB接口的智能電話設計中的應用實例。

設計實例

圖2所示為典型的LCD屏的“寫”操作,此處采用基于LpLVDS或CTLI/O技術的uSerDes,從基帶處理器向LCD顯示器傳遞RGB數據。這是雙處理器的翻蓋式智能電話設計中一種典型RGB接口。使用LpLVDS技術或CTL技術,應用處理器上LCD接口輸出的16位TTL并行數據總線,被串行化成單一高吞吐量差分數據流(D+和D-)。這種設計不僅有效地降低電磁干擾,而且因為省去了機體和翻蓋之間大量電纜和連接器,所以成本也得以顯著降低。此外,由于LpLVDS和CTL技術的電磁干擾輻射超低,因此無需采用電磁干擾濾波器,進一步降低了成本。

本文小結

隨著未來3G手機的高分辨率顯示器和相機等多媒體應用需求的增長,設計人員將逐漸從現時的并行TTL接口技術轉向差分串行互聯技術。具有低電磁干擾、高吞吐量、低功耗、抗噪聲干擾等特性的接口技術,將成為超便攜和消費產品市場的重要組成部分,而這些產品市場包括了手機、攝像機、打印機,以及其它對功率和電磁干擾有限制的顯示終端。

電焊機相關文章:電焊機原理

評論