基于TMS320C64x的MPEG-4實時編碼器設計與實現

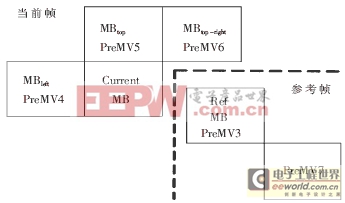

圖3 預測運動矢量示意圖

(2)確定篩選候選值的依據——SAD(絕對誤差和)的門限值ThreshSAD。

SAD是確定最佳匹配塊的準則。門限值ThreshSAD是指這樣一個值:如果參考幀內某一宏塊和當前宏塊的SAD小于ThreshSAD,則當前宏塊的MV值就可取作二者之間的位移。因此,ThreshSAD就可作為篩選7個候選值的依據。

由于SAD在空間上的相關性,ThreshSAD由相鄰宏塊的SAD值來確定:

ThreshSAD=Min{SADleft,SADtop,SADtop_left}

其中,SADleft、SADtop、SADtop-right分別為MBleft、MBtop、MBtop-right和其對應匹配塊的SAD值,ThreshSAD取三者的最小值。

(3)從7個候選值中選出當前宏塊的MV值。

按照PreMV1~7的順序,依次計算當前宏塊和7個匹配塊的SAD值。如果有SAD值小于ThreshSAD,即停止計算,選用對應的PreMV作為當前宏塊的MV值;如果7個SAD值均大于ThreshSAD,則采用運動搜索來確定當前宏塊的MV值。該運動搜索并不以MV=(0,0)為中心,而是以對應SAD值最小的PreMV為中心,搜索采用簡化的菱形算法。

對標準視頻序列foreman.cif(352×288)進行編碼(碼率300kbps),測得表1所示數據。采用預測的運動估計算法利用視頻序列在時間和空間上的相關性,無需對每個宏塊都進行運動搜索,而且其搜索中心點也同樣利用了相關信息,搜索算法也可進一步簡化,因此大大減少了運動估計的計算量;同時,預測有助于提高圖像質量,直接進行快速運動搜索通常會帶來局部最小的問題,從而影響圖像質量,而PreMV1~7取自位于當前宏塊周圍各個方向的宏塊的MV值,避免陷入局部最小。

表1 預測技術對運動搜索性能的提高

| 采用預測 | 平均每個宏塊所需的 SAD值計算次數 | 峰值信噪比PSNR(dB) | 平均幀率(fps) |

| 是 | 5 | 33.16 | 120 |

| 否 | 15 | 33.23 | 95 |

3 基于C64x CPU的軟件優化技術

為了提高代碼的執行效率,必須充分利用C64x CPU的VLIW和流水線結構對其進行優化,使程序無沖突地并行執行。MPEG-4編碼程序中包含大量的循環體,例如計算SAD值、量化、DCT、半像素插值、運動補償和構建重建幀等。這些循環體代碼并不復雜,但執行次數頻繁,占據了編碼的絕大部分時間,因此循環體的優化是重點。本文所采取的代碼優化分為C語言優化和編寫線性匯編兩個步驟,主要從消除數據相關性、數據打包和循環體的軟件流水三個方面進行優化。

3.1 針對C語言的優化

C代碼的優化主要依靠開發環境CCS的編譯器完成,編程者需要合理選擇編譯選項,并利用特定的關鍵字和指令向編譯器提供優化信息。例如關鍵字restrict用來消除數據間的相關性,編譯器從而可以安排語句的并行執行;內聯函數_nassert有助于數據的打包處理;宏指令#pragma MUST_ITERATE告訴編譯器有關循環迭代次數的信息,編譯器會根據這一信息進行軟件流水。

3.2 用線性匯編改寫關鍵代碼

線性匯編是TMS320C6000特有的一種編程語言,介于高級語言和匯編語言之間。它可以指定指令用到的寄存器和功能單元,更易于對數據的打包處理。

線性匯編代碼的并行處理和軟件流水由匯編優化器完成,編程者需要熟悉C64x DSP的CPU結構和指令集,認真設計代碼并充分利用編譯器的反饋信息合理修改代碼,才能寫出高質量的線性匯編。本設計中程序主框架采用C語言編寫,其它各關鍵部分的代碼采用線性匯編實現。表2是代碼優化前后的效率對比,表2中所列各代碼段均針對8×8宏塊進行處理。

表2 各關鍵代碼優化前后消耗指令周期數對比

| 代碼段 | 未優化 | C優化后 | 線性匯編優化后 |

| SAD值計算 | 1400 | 55 | 34 |

| 量化 | 1250 | 238 | 108 |

| 逆量化 | 1200 | 291 | 170 |

| FDCT | 1360 | 292 | 96 |

| IDCT | 1600 | 373 | 102 |

| 半像素插值 | 2800 | 466 | 246 |

| 運動補償、做差 | 1950 | 160 | 59 |

| 重建宏塊 | 1000 | 890 | 88 |

4 結果分析

對各標準視頻序列進行編碼,測得表3所示數據。實時采集D1(720×576)分辨率的視頻進行編碼,測得碼率為850kbps時,編碼速率達25fps以上,峰值信噪比(PSNR)高于31dB,實現了高分辨率的實時MPEG-4編碼。

表3 標準視頻序列的編碼結果

| 視頻序列 | 分辨率 | 碼率(bps) | PSNR(dB) | 平均幀率(fps) |

| News | QCIF | 100k | 36.23 | 480 |

| Silent | QCIF | 100k | 35.66 | 485 |

| Foreman | QCIF | 100k | 32.04 | 465 |

| Foreman | CIF | 300k | 33.16 | 120 |

表3中各視頻序列的編碼均采用了8×8半像素精度的運動估計,解碼圖像的視覺效果較好。對于較低分辨率的視頻(QCIF、CIF),其編碼速率已遠遠高于實時的要求,因此可以考慮添加新的算法以提高壓縮效率并增強碼流的抗差錯性能。

本文以DM642芯片為例詳述了基于C64x DSPs的MPEG-4實時編碼器設計。編碼器采用MPEG-4 Simple Profile算法,在算法和代碼優化方面還有一定的研究空間。本文給出的設計方法可以進一步推廣到H.264或者其他視頻編碼系統。

參考文獻

1 Prasad RSV, Ramkishor korada. Efficient implementation of MPEG-4 video encoder on RISC

core[J].IEEE Transactions on Consumer Electronics, 2003;47(1):1~6

2 A. Dasu, S. Panchanathan. A Survey of Media Processing Approaches[J]. IEEE Trans.on

Circuit and System for Video Technology, 2002;12(8):1~13

3 Tihao Chiang, Hung_Ju Lee, Huifang Sun. An overview of the encoding tools in the

MPEG-4 reference software[J].In-ternational Symposium on Circuits and Systems,

2000; May 28-31:1~4

4 鐘玉琢,王 琪,賀玉文. 基于對象的多媒體數據壓縮編碼國際標準——MPEG-4及其校驗模型[M].

北京:科學出版社,2000

5 李方慧,王 飛,何佩琨. TMS320C6000系列DSPs的原理與應用[M].北京:電子工業出版社,2003

評論