PCI總線目標控制器的設計

狀態機共分為10個狀態,下面對每個狀態的意義及狀態跳轉條件的詳細說明:

目標空閑(idle):當PCI總線有新的命令但控制器正忙于未完成的數據傳輸或寄存器配置時,狀態機跳轉到check_abort;控制器空閑但寄存器內有記錄的未完成的讀操作,狀態機跳轉到check_addr;PCI總線上有數據傳輸要求而又未出現上面的兩種情況,狀態機跳轉至cmd_start。

啟動命令解碼(cmd_start):滿足放棄條件如奇偶校驗錯誤、強制放棄等條件時,狀態機跳轉至start_abort;不滿足放棄條件,若目標設備沒有突發傳輸能力,狀態機跳轉至start_single,若目標設備有突發傳輸能力且主設備發起的是寫命令,狀態機跳轉至start_multiple,如果目標設備有突發傳輸能力且主設備發起的是延遲讀命令,狀態機跳至start_retry;上述情況均未發生,狀態機跳轉至start_wait_rd1。

檢查地址匹配(check_addr):滿足放棄條件如奇偶校驗錯誤、強制放棄等條件時,狀態機跳轉至start_abort;如果地址與之前的請求地址一致,對目標設備進行延遲讀,狀態機跳轉至start_multiple;如果地址不一致狀態機跳轉至start_retry。

放棄條件檢測(check_abort):滿足放棄條件如奇偶校驗錯誤、強制放棄等條件時,狀態機跳轉至start_abort;不滿足條件,狀態機轉至start_retry。

讀等待狀態1(start_wait_rd1):如果FIFO中有了待傳輸的數據,狀態機跳轉至start_wait_rd2;否則一直等待在狀態start_wait_rd1。

讀等待狀態2(start_wait_rd2):FIFO中已經有了所要讀取的數據,狀態機跳轉至start_multiple。

目標設備放棄(start_abort):一直維持該狀態直到主設備聲明傳輸結束,狀態機轉至idle。

單數據傳輸(start_single):如果主設備聲明最后一個數據傳輸,狀態機跳轉至idle;如果主設備繼續對該目標設備進行讀寫操作,狀態機跳轉至start_retry。

數據突發傳輸(start_multiple):如果剩下最后一個字節傳輸,狀態機跳轉到idle;如果地址信息無效或地址越界,狀態機跳轉到start_retry;如果接收FIFO幾乎滿了而PCI主設備繼續往其中寫入數據,狀態機跳轉到start_retry;其它情況狀態機保持start_multiple狀態不變。

重試(start_retry):一直維持該狀態直到主設備聲明傳輸結束,狀態機轉至idle。

3數據通路實現

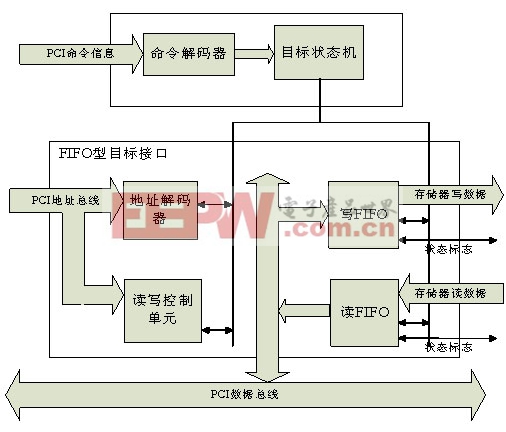

目標控制器的數據通路具體可通過兩種類型的目標接口實現:寄存器型目標接口和FIFO型目標接口。

3.1寄存器型目標接口

每個PCI功能擁有64個配置雙字的單元[1](前16個雙字的格式和用法由PCI規范預定),保留用于實現配置寄存器。本地可以有一些功能設備,這些設備都有相應的控制/狀態寄存器,PCI總線上的主設備要對這些控制寄存器進行編程,進而控制相應的功能設備完成特定功能。兩類寄存器可以歸為一個數據通道實現,寄存器型目標接口就為本地的功能設備提供了這樣一種接口,使得PCI總線上的主設備可以通過它來訪問功能設備的寄存器。由于PCI總線主設備的訪問目標是一些寄存器,所以該接口無需支持突發傳輸,主設備每一次訪問最多只涉及到32位的數據傳輸。

3.2FIFO型目標接口

FIFO型的目標通道主要用于大量的數據傳輸,可以將本地的存儲器掛接在該接口上,這樣PCI總線主設備可以通過FIFO型目標通道訪問到本地的存儲器,針對PCI主設備對本地存儲器的讀和寫操作,設置了兩個異步FIFO,讀FIFO和寫FIFO。其結構如圖3

命令解碼器和目標狀態機組成了該接口的控制單元。FIFO型目標接口由地址解碼器、讀寫控制單元和讀/寫異步FIFO四部分組成,在控制部件的協調控制下,共同完成PCI總線上的其它主設備對本地存儲器的數據存儲或讀取。

讀寫控制單元:主要用于目標延遲讀的控制,存儲并比照前后數據傳輸請求的地址和命令信息,聲明本次傳輸請求是否為有效的延遲讀請求。

讀/寫FIFO:異步FIFO,用于緩存PCI主設備到本地存儲器的讀寫數據。

地址解碼器:解碼PCI總線上的地址信息,識別對FIFO型目標接口的訪問。對于地址解碼器的實現,在最初PCI系統分配地址時,FIFO型的目標接口被分配到某一段地址區內,通過地址翻譯將其映射到本地的系統中[4]。

圖3FIFO型目標接口邏輯結構

對PCI主設備發起的寫操作,數據會先以PCI時鐘寫入接口內的寫FIFO,同時PCI控制器會通知本地存儲器控制器有數據寫入。本地存儲器控制器待FIFO中達到一定數據量時以自己的時鐘讀取FIFO中的數據存入本地存儲器,如果FIFO讀空,存儲器會暫停等待直到FIFO中有新的數據寫入,才進行讀取。

對PCI主設備發起的讀本地存儲器的操作,為了提高讀數據的效率,設計中根據不同數據傳輸的特點,把讀操作劃分為兩個類型,即立即讀和延遲讀。

(1)立即讀:在PCI總線主設備發起讀操作后,一直占用PCI總線等待,PCI總線控制器向本地存儲器請求對應的數據,直到本地存儲器將數據寫入讀FIFO中,PCI控制器讀取FIFO中數據開始PCI總線上的數據傳輸。這種讀類型一般適用于進行數據量小的傳輸且本地存儲器可以在較短的時間內將要求的數據送到PCI總線。

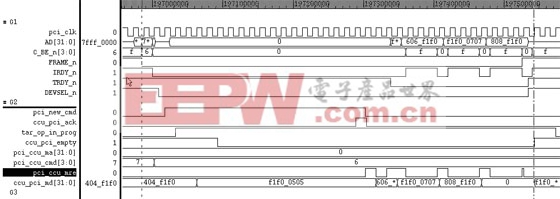

(2)延遲讀:PCI總線主設備的讀請求到達PCI目標總線控制器時,控制器鎖存地址和命令信息,并回應主設備讓它重試。同時PCI目標總線控制器向本地存儲器請求數據,本地存儲器將數據寫入總線控制器中的FIFO中。此時如果PCI總線上的主設備重試先前的數據傳輸請求,PCI目標控制器就可以響應請求將數據發送到PCI總線上。這個過程中,PCI總線主設備在收到重試回應后就會釋放PCI總線,允許其它的主設備占用總線進行數據傳輸,這樣從而提高了總線的利用率。圖4給出了PCI主設備突發讀時采用延遲讀的仿真結果圖

圖4突發讀時仿真波形

4結束語

本文基于PCI2.2總線規范完成了通用PCI目標控制器的RTL級設計。經驗證設計完全實現了目標控制器的功能,目前已通過了FPGA原型驗證并應用到CMOS圖象傳感器的數據傳輸中。在后續的開發中,可以考慮在控制器內部加入電源管理模塊,進一步降低PCI目標控制器的功耗。

本文的創新點:該設計方案將目標控制器整體分為控制邏輯和數據通道兩部分,并根據目標設備的不同類型,在數據通道內實現不同的目標接口,并引入了立即讀和延遲讀機制實現數據傳輸,使整個設計取得了較高的效率。

參考文獻

[1]TomShanley,DonAnderson著.林輝等譯.PCI系統結構.電子工業出版社,2000.

[2]沈涵飛,甘萌.PCI總線目標控制器的設計與實現[J].計算機工程與設計.2004,25(11):2101~2104

[3]施少敏,馬彥恒.基于接口芯片PCI9030的PCI總線接口卡的設計[J].微計算機信息.2006,11-2:295~297

[4]TinooshMohsenin.DesignandEvaluationofFPGA-BasedGigabit-Ethernet/PCINetwordInterfaceCard.MasterDegreeDissertationofRice

University.2004:71~74

[5]JanickBergeron,WritingTestbenches-FunctionalVerificationofHDLModels.Boston,KluwerAcademicPublisher,2000.

評論