USB 3.0主控端系統(tǒng)設計應用

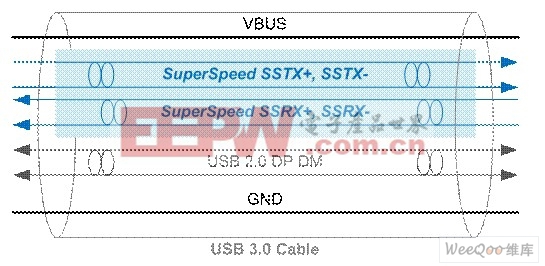

現(xiàn)有的USB 2.0纜線及連接器提供了四條信號線,包含VBus 5V 500mA直流供電,一對DP/DM半雙工雙向差分信號線,以及GND接地,以此四條接線提供了USB 2.0的480Mbps的資料傳輸,及直流供電。USB 3.0為了提供高達5Gbps的資料傳輸率,額外增加五條訊號線,包括兩對單向傳輸?shù)某咚伲⊿uperSpeed)差分訊號:SSTX+, SSTX-, SSRX+, SSRX-,及多一組的接地接點,并將直流供電能力提升至5V 900mA。其中的兩對差分訊號分別負責傳輸及接收,提供雙向全雙工的5Gbps的傳輸能力。

圖1:USB 3.0連接器,后排的USB 3.0 SuperSpeed信號接點

圖2:USB 3.0纜線示意圖,藍色部分為SuperSpeed 5Gbps信號

SuperSpeed 5Gbps信號品質(zhì)的系統(tǒng)設計及量測挑戰(zhàn)

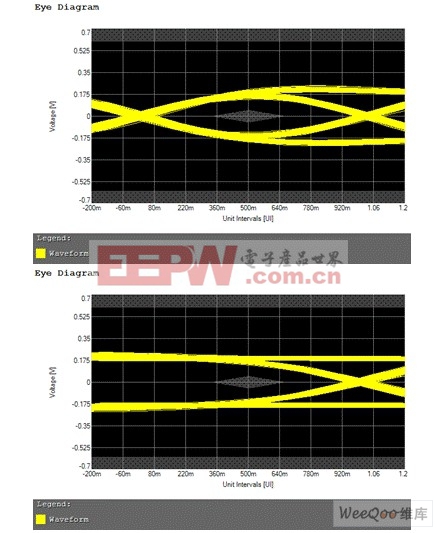

USB 3.0 SuperSpeed位傳輸率高達5Gbps,且采用開放式接口,信號品質(zhì)將直接影響裝置兼容性及傳輸效率,與使用者體驗息息相關。主控芯片、印刷電路板、連接器、纜線甚至裝置端芯片組,都是影響信號品質(zhì)的關鍵。對于芯片廠商的類比傳輸設計能力,半導體制程變異,系統(tǒng)廠商的印刷電路設計布局都是全新的考驗。不同于USB 2.0的經(jīng)驗,信號品質(zhì)的參考指標將不再只是傳輸端的眼圖(Eye diagram)。USB 3.0獨立的傳輸及接收通道,系統(tǒng)接收能力也成為信號品質(zhì)及系統(tǒng)設計的重要量測指標。接收端量測主要考驗待測物對不同頻率的時基誤差容忍能力。容忍能力越強的芯片,代表其系統(tǒng)設計可較寬松,可使用較長的信號走線,也有較佳的裝置兼容性。

圖3: USB 3.0 SuperSpeed傳輸端信號量測眼圖(Eye diagram)

評論