基于DDS與USB技術的通信對抗教學演示系統(tǒng)中硬件的設計與實現(xiàn)

1概 述

擴展頻譜通信具有抗干擾能力強、隱蔽性好等優(yōu)點,已成為通信對抗與反對抗中最重要的技術手段,在軍事通信中日益受到重視,跳頻電臺就是擴頻通信在軍事領域中的重要應用。在通信對抗中如何有效地對抗跳頻電臺是目前的一個熱點問題。在通信對抗的教學中為了以實驗的形式向人們展示跳頻通信中干擾與抗干擾的原理,并能對跳頻通信進行偵察和實施多種干擾的效果進行比較,為科研中尋找對跳頻通信的最有效干擾方式提供有效的數(shù)據(jù)和參考,本文給出了一種基于DDS與USB技術的通信對抗教學演示系統(tǒng)中硬件方案的設計與實現(xiàn)。

2 系統(tǒng)整體結構設計及原理說明

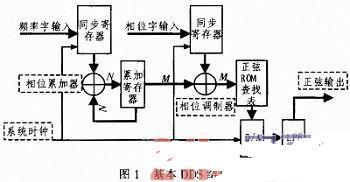

系統(tǒng)主要由控制計算機、發(fā)射機、電子偵察模塊、電子干擾模塊和接收機等五部分組成,如圖1所示。計算機主要是用于控制與協(xié)調各個模塊的工作和數(shù)據(jù)傳輸,決定系統(tǒng)各部分的工作模式并對工作狀態(tài)進行實時監(jiān)視。

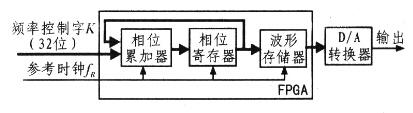

發(fā)射機在計算機指令的控制下,在指定的工作頻段內以相應的方式發(fā)射跳頻信號。電子偵察模塊利用高速A/D采樣技術與高速FFT實時處理技術可以快速地捕捉并計算出發(fā)射信號的工作頻率點,同時將偵察到的跳頻數(shù)據(jù)送至電子干擾模塊。接收到偵察數(shù)據(jù)的干擾模塊在計算機控制下利用FPGA控制頻率合成器件產生各種調制信號,選擇不同的干擾方式對通信電臺實時有效的干擾。干擾信號與實際跳頻信號分別送人合路器中,由合路器送至接收機比較各種不同干擾方式的實際效果。

3器件的選擇

3.1 A/D芯片與FPGA芯片

A/D芯片選用的是為寬帶和多信道數(shù)字無線接收機系統(tǒng)而推出的12位中頻快速采樣芯片AD6640。

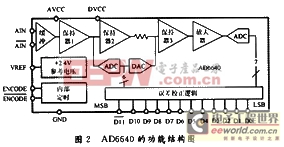

AD6640是一個高速度、高性能、低功耗,單片式12位AD轉換器,內含采樣保持電路和基準源。他由單電源+5 V供電,TTL/CMOS兼容電平輸出,中頻采樣頻率的典型值為70 MHz(多信道時)和200 MHz(單信道時),采樣速率可達65 Mb/s,信噪比SNR的典型值為68 dB,SFDR值為80 dB,功耗為710 mW。AD6640采用兩級子區(qū)式的轉換結構,既保證了精度又降低了功耗,其功能模塊如圖2所示。從圖2可以看出ADC所有需要的功能,包括輸入緩沖,跟蹤保持放大,數(shù)字糾錯以及2.4 V參考電壓都由芯片提供,從而使其設計變得更輕松。

FPGA芯片采用的是Altera公司的ACEXlK系列產品的EPlKl00芯片。其特點是將查找表(LUT)和EAB相結合,提供了高效率而又廉價的結構。基于LUT的邏輯對數(shù)據(jù)路徑管理、寄存器強度、數(shù)學計算或數(shù)字信號處理(DSP)的設計提供優(yōu)化的性能和效率,而EAB可實現(xiàn)RAM,ROM,雙口RAM或FIFO功能。這使得ADEXlK適合于復雜邏輯及存儲器功能,如數(shù)字信號處理、寬域數(shù)據(jù)路徑管理、數(shù)據(jù)變換和微處理器等各種高性能通信應用。基于可重構CMOS SRAM單元,ACEX1K結構具有實現(xiàn)一般門陣列宏功能需要的所有特征,相應的多引腳數(shù)提供與系統(tǒng)元器件的有效接口。先進的處理功能和2.5 V低電壓要求,使得AC2EX1K器件滿足廉價、高容量的應用需要。

3.2 DDS芯片

DDS芯片選用的是美國的Analog Device Inc(ADI)公司生產的DDS器件AD9854。AD9854數(shù)字頻率合成器是一個采用了先進的DDS技術的高集成器件。

他具有一對內部高速、高性能的正交D/A轉換器和比較器,可實現(xiàn)數(shù)字合成正交的I和Q路輸出。當輸入一準確的參考頻率,AD9854即可產生一高穩(wěn)定的頻率、相位、幅度可編程的正弦和余弦信號。AD9854的DDS核心具有48 b的頻率分辨率。14 b相位截斷保證了優(yōu)良的SFDR指標。AD9854的電路工藝使同步正交信號輸出的頻率最高達到150 MHz,平均每秒產生1百萬新頻率。AD9854中4~20整數(shù)倍的可編程參考頻率累加器能使外部輸入的低速時鐘轉變成內部高速時鐘(最高300 MHz)。

AD9854能實現(xiàn)除了基本的FSK以外的增強頻譜特性的Ramped FSK。該器件采用了先進的35μmC2MOS技術使該器件只需要+3.3 V的電源供應。

3.3 DAC芯片與USB芯片

系統(tǒng)所用的DAC為ADI公司的AD5344,他是一種低功耗12 b數(shù)模轉換器。該芯片可應用于便攜式電池電源儀器、可編程電壓和電流源、可編程衰減器、工業(yè)處理控制器以及數(shù)字放大和補償調節(jié)等方面。圖3為其內部結構原理圖。AD5344有4路12 b DAC,可在2.5~5.5 V之間正常工作,在外接+3 V電壓時典型電流值為500μA,并且具備進一步將電流降至80 nA的節(jié)電模式。他的輸出緩存可將輸出驅動到兩個電源軌道之上。通過A0和A1可控制選擇哪一路輸出。

評論