基于多環鎖相寬帶細步進頻率合成器的設計

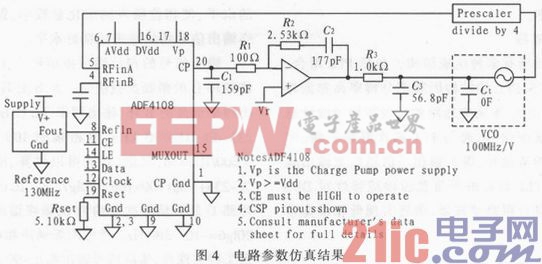

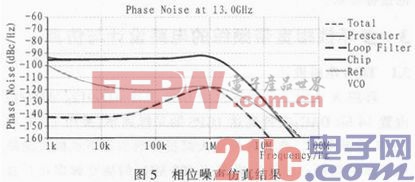

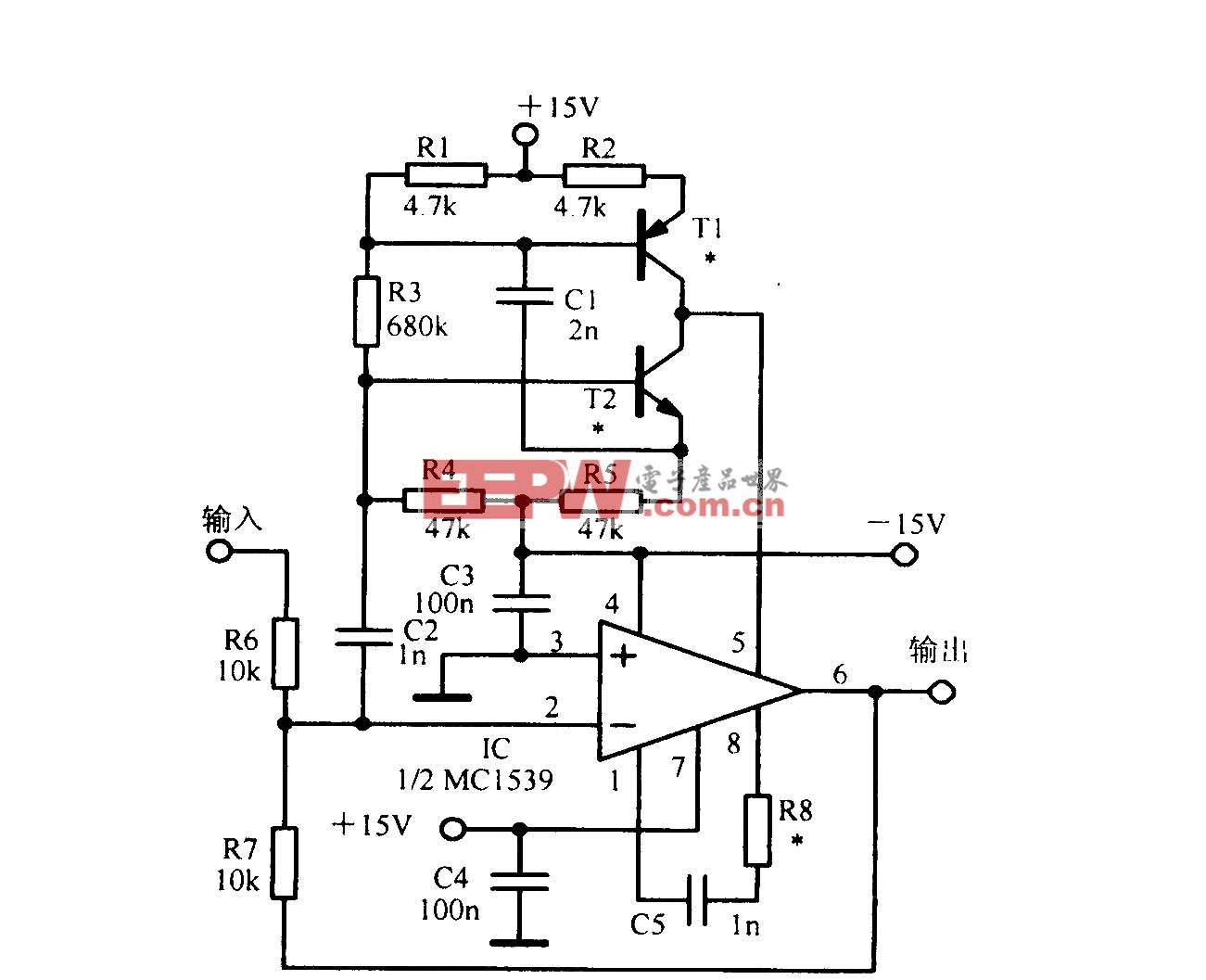

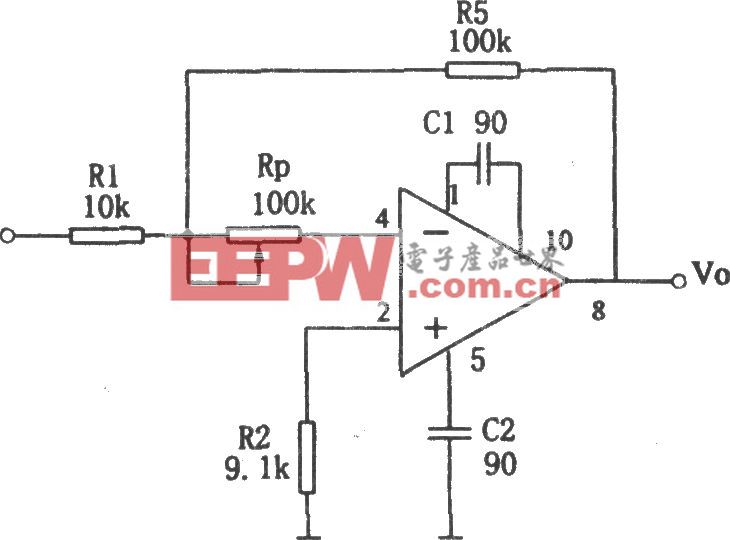

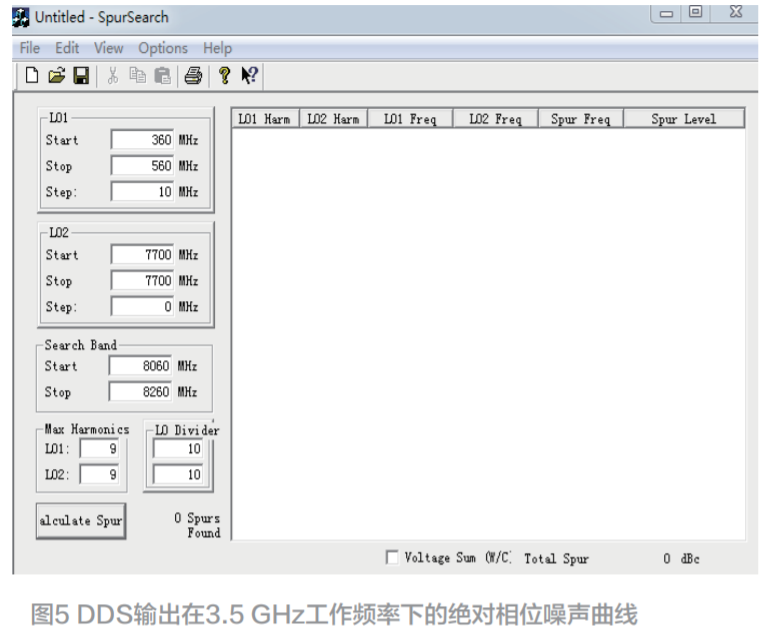

末級鎖相環路D采用ADI公司鎖相環芯片AD4108。該芯片工作頻率達8 GHz,控制簡單、功耗極低,同時具有良好的噪聲基底性能。經軟件仿真,末級鎖相環路電路參數及輸出相噪如圖4,5所示。

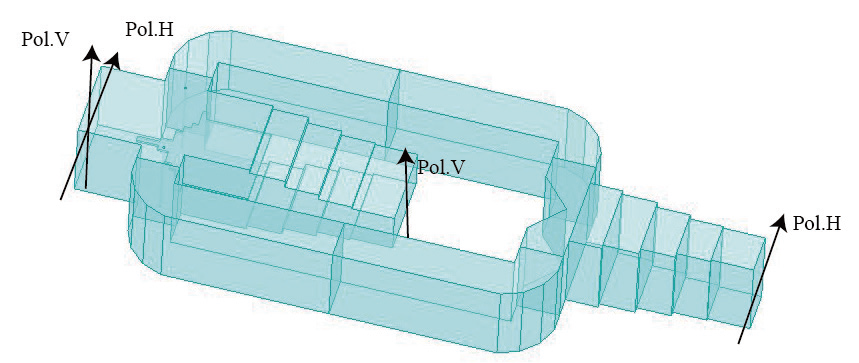

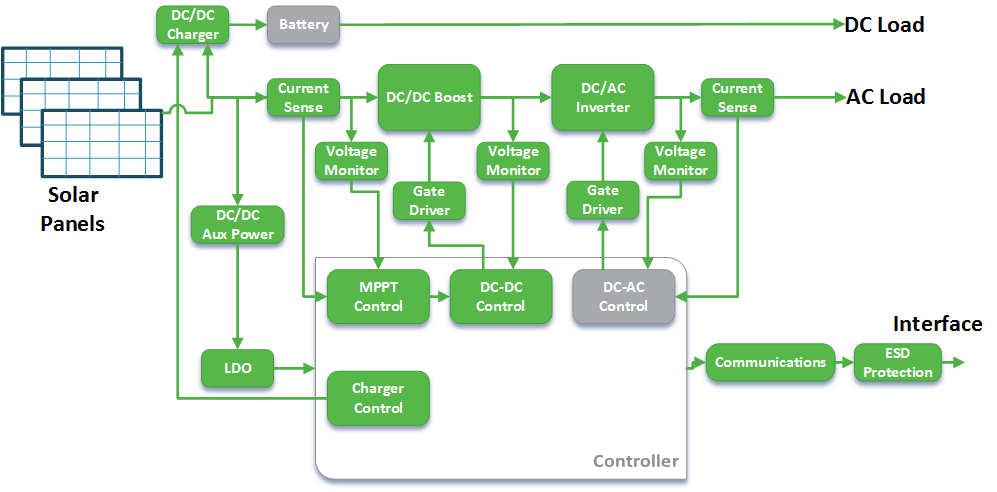

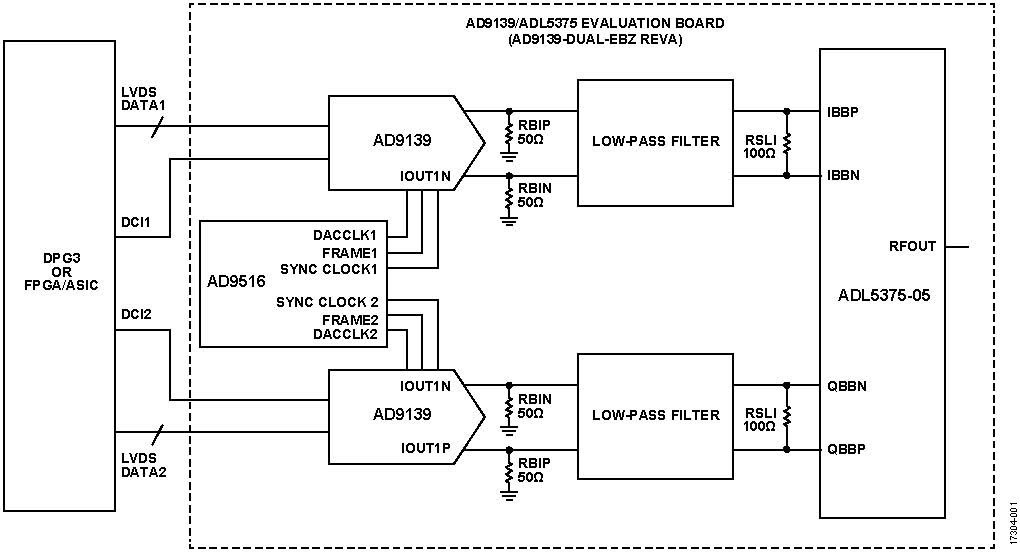

整個多環鎖相電路結構比較復雜,包含鎖相電路及數字控制電路等。為保證輸出信號相位噪聲和雜散抑制性能,結構設計中采取了多腔體分隔的結構,并注意微波吸收材料的使用,保證各個功能環路工作穩定且整體電磁兼容性能良好。

4 電路調試與測試結果

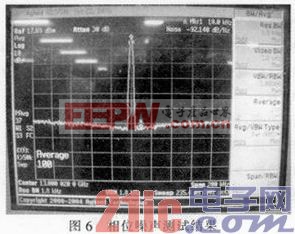

由于合理的方案設計和準確仿真,相位噪聲等主要指標均可實現。如圖6所示,全頻段輸出信號相位噪聲可達到-92 dBc@1kHz;-92 dBc @10kHz。

由于各功能環路輸出中間頻率信號較多,雜散控制是調試難點。在測試中發現,有少數頻點的近端有雜散較大,主要分布在參考100 MHz整數倍附近的細步進頻段,經分析,該類雜散的產生主要是由于環路A中DDS輸出信號與參考信號100 MHz及其諧波經鏈路泄露或空間輻射進入混頻器及鑒相器中,產生的高階交調出現在輸出信號近端,由于分布在鎖相環路帶寬以內,難以消除。該現象的產生說明,多環鎖相的細步進頻綜對模塊內部各功能單元的電磁屏蔽與隔離要求非常高。通過調試分析,可通過改變A、C環路輸出頻率和環路D的倍頻次數N的方法規避和解決。根據公式(2),通過掃頻,一旦發現存在近端雜散的頻率點,通過改變fDDS、fLO2和末級鎖相環倍頻次數N的頻率組合,同樣可以實現相同頻率的輸出,且fDDS發生改變,與100 MHz的高階交調雜散分布遠離主信號中心,可被末級鎖相環路濾波器濾除。圖7為經過后期頻率控制程序處理前后的雜散分布對比圖,可見主信號近端雜散已經明顯消除。

經不斷調試改進,各項指標最終測試結果如表1,均滿足設計指標要求。

5 結 論

文中介紹了基于多環結構的鎖相寬帶頻率合成技術,在實現細頻率步進和低雜散的指標要求情況下,相位噪聲可達到≤-92 dBc/Hz@1 kHz,滿足系統對高質量頻率合成器的需求,具有較好的應用前景。

dc相關文章:dc是什么

低通濾波器相關文章:低通濾波器原理

分頻器相關文章:分頻器原理 鑒相器相關文章:鑒相器原理 鎖相環相關文章:鎖相環原理 鎖相放大器相關文章:鎖相放大器原理

評論