電源瞬時波動對微機的影響及防護

近年來,微機系統在工業自動化,生產過程控制,智能化儀器儀表等領域的應用越來越深入和廣泛,有效地提高了工作效率,改善了工作條件。但是由于電磁環境的日趨惡劣和復雜,其工作的可靠性和安全性受到了嚴重威脅。最常見也最嚴重的一種干擾源就是市電電網頻繁出現的瞬時掉電和下跌,他可使微機系統程序亂飛,控制失誤,造成重大損失或傷亡事故。因此,研究電源瞬時波動對微機系統的影響,提高系統的電磁兼容性,有很高的實用價值。

1 電源瞬時波動形成的原因及其對微機系統的影響

1.1 電源瞬時波動形成的原因

電源瞬時波動主要是指電網電壓的瞬時下跌和瞬時停電。瞬時下跌是指電網電壓幅值因某種原因在某一瞬間突然降低;瞬時停電是指電網電壓在某一瞬問突然完全為零。

電網電壓瞬時波動的原因很多。例如,當電網遭到雷擊或雷電感應時,可造成不小于0.1 s的瞬時停電,絕大多數情況可達0.3 s以上。電力輸送線方面的事故也是產生電網電壓瞬時波動的一個主要原因,90%的電力線事故會導致電網有5~8個周期的瞬時停電[1]。工業現場的大功率設備啟動運行時形成相當大的沖擊電流,該電流是正常工作電流的10~40倍,他可以引起局部電網電壓的瞬時波動,有的大功率電機啟動時,會導致附近電網電壓瞬時

下跌20%,持續30個周期之久[2]。

1.2 電源瞬時波動對微機系統的影響

電網電壓的瞬時波動可直接導致系統內部電源電壓的瞬時下跌,對微機系統的工作造成嚴重干擾,主要表現在以下幾個方面[3]:

使數據采集誤差加大;引入虛假狀態信號,使控制狀態失靈;破壞RAM存儲器的數據;改變PC值,使程序運行失常。

2 對電源瞬時波動干擾的防護

2.1采用快速交流穩壓器

采用快速交流穩壓器可輸出穩定的220 V交流電,從而消除電網電壓瞬時波動對微機系統工作的影響。

2.2 采用不間斷電源UPS

不間斷電源UPS能夠在電源停電或下跌時,由內部逆變電源給微機供電,他能有效地防止電網的瞬時停電或電網電壓的瞬時跌落。在要求較高的微機系統中,UPS是必不可少的設備。

2.3 加大系統內部整流電路的平滑電容和采用后備電源

增大整流電路的平滑電容,在一定程度上可消除電網電壓瞬時波動的影響。當平滑電容為470μF時,可承受O.5個周期20%下跌幅度的瞬時波動;當電容為4 700μF時,可抵抗6.5個周期100%下跌幅度的瞬時波動。

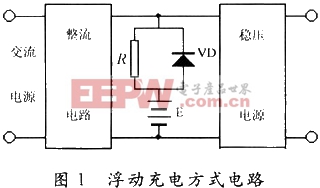

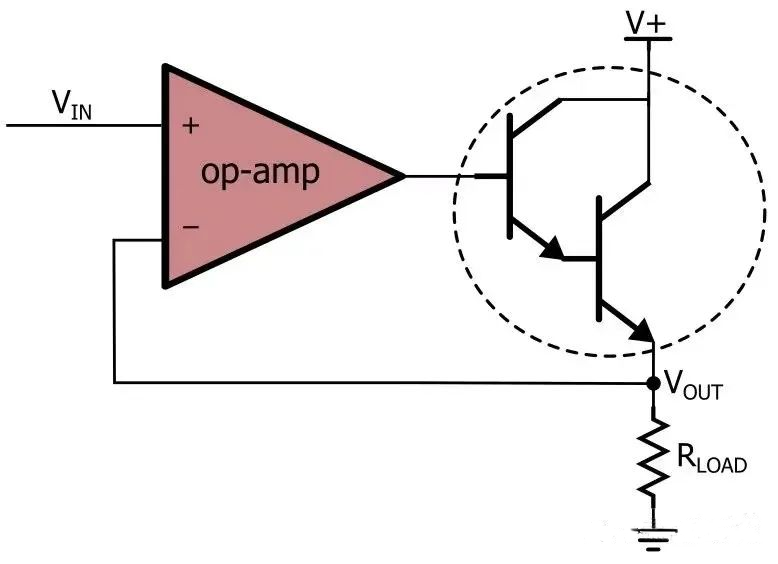

對持續時間較長的波動,只靠增大電容是不行的,這時應考慮用輔助電源。采用浮動充電方式的輔助電源的配置如圖1所示。正常工作時,整流電路輸出的脈動直流電源經R給電池E充電;當瞬時波動發生時,電池經二極管給系統供電,大大提高了系統抗電源波動干擾的能力。不僅如此,由于電池相當于一個性能良好的旁路電容,他對10 kHz~1 MHz頻率成份的噪聲衰減有顯著效果。

2.4 利用系統本身功能消除電源瞬時波動的影響

由于交流穩壓器和UPS的造價高,配置麻煩,要求不高的微機系統一般不采用上述措施,而是利用系統本身功能,采取預先檢測手段,在瞬時波動還沒有影響到系統工作時,使其迅速回到開機時的初始狀態。

一般微機系統都有一個開機自動復位電路,他利用一個RC充電電路,使復位電平的建立遲于電源的建立,從而避免開機時CPU的工作混亂。

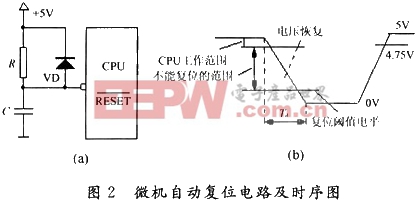

當電源瞬時停電時,+5 V供電因停電而很快下降,電容C通過VD放電。自動復位電路及瞬時停電時電容C的電壓波形如圖2所示[4]。當電容C上的電壓下降到低于4.75 V后,由于仍高于復位閾值電壓,并不能使CPU復位,這時RAM中數據將遭到破壞。因此,只依靠簡單的RC復位電路不能解決電源瞬時波動所帶來的問題。

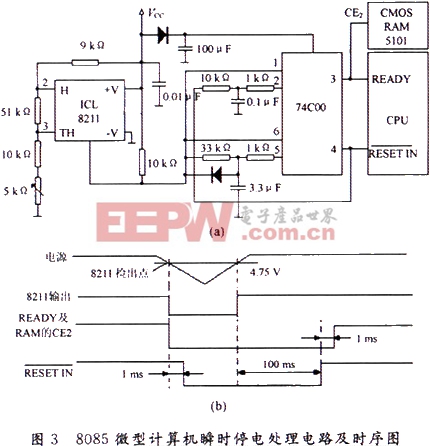

解決這種問題的方法是增加瞬時停電檢測電路。圖3是一個微機系統的復位信號輸入電路及時序圖。當Uc低于電壓檢測值時,8211輸出為低,使CPU的READ-Y和CE2最先為低,CPU停止工作,RAM與數據總線隔開。1 ms后,復位信號變低,使系統復位。電源復位后,

8211輸出為高,再過100 ms復位信號變為高電平,這樣可使CPU避開電源電壓剛升至4.75 V后的不穩定工作區,復位信號為高后1 ms,READY和CE2變高,CPU開始正常工作。

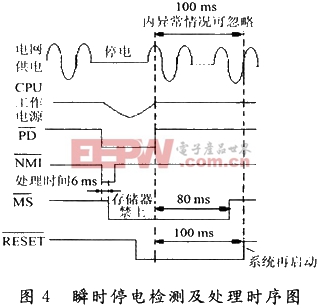

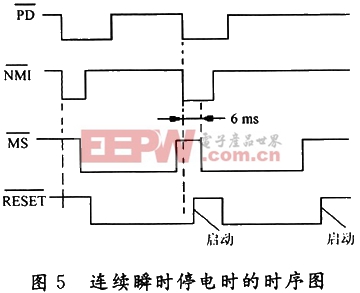

更完善的措施是,不僅保護RAM內容,而且還進行人棧操作,然后再讓CPU停止工作。當電源恢復時,再從堆棧中取出數據,使程序繼續進行下去,而不是重新開始。圖4是某微機處理電源瞬時停電的各種信號時序圖。電源瞬時停電時,停電信號PD為低,觸發單穩電路產生一個負脈沖送至CPU的NMI端,CPU響應中斷,自動產生RST指令,把PC中下一條要執行指令的16位地址送入堆棧保存,同時在NMI變低后6 ms產生禁止存儲器工作的MS信號。當電源恢復后80 ms,MS信號變高,最后復位信號變高,系統再次啟動。該方案還可以忽略電源恢復后100 ms內電源的再次波動。

但是實際的停電情況相當復雜,并不是單純的一次性停電,而是象振蕩一樣,重復好幾次。當第一次停電恢復后,MS信號變高,其后,RESET信號也變高。在系統剛要啟動時,第二次停電又產生了,NMI再次變低,如圖5所示。這時的中斷申請等于被忽視,因為他并不能做出停電處理,將數據進行入棧操作,而且,因MS信號已變高,在第二次停電發生6 ms內存儲器也不能被禁止。在此期間系統卻發生了再啟動,CPU將第一次停電時人棧的數據從堆棧中取出,開始停電前的程序作業。而在第二次停電恢復正常時也同樣從堆棧中取出數據。由于忽視了一次NMI信號,少了一次入棧動作,所以整個程序就亂了。解決這個問題的辦法是,保證在停電信號后6 ms內CPU不進行任何處理。這樣即使再有停電情況發生也不會進行棧操作,再啟動時,取出的就是第一次停電時的入棧數據。

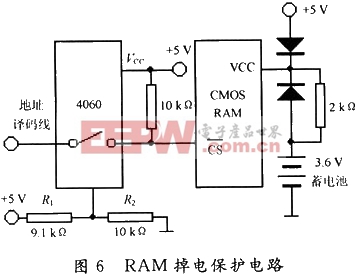

為確保RAM數據不遭破壞,建議使用非易失性RAM(NVRAM)及E2PROM等專用存儲器。另一種方法是在計算機內部加裝專給RAM供電的后備電源,RAM采用CMOS靜態讀寫存儲器,這種存儲器在斷電時只需2.0 V電源就可以維護信息不被丟失。

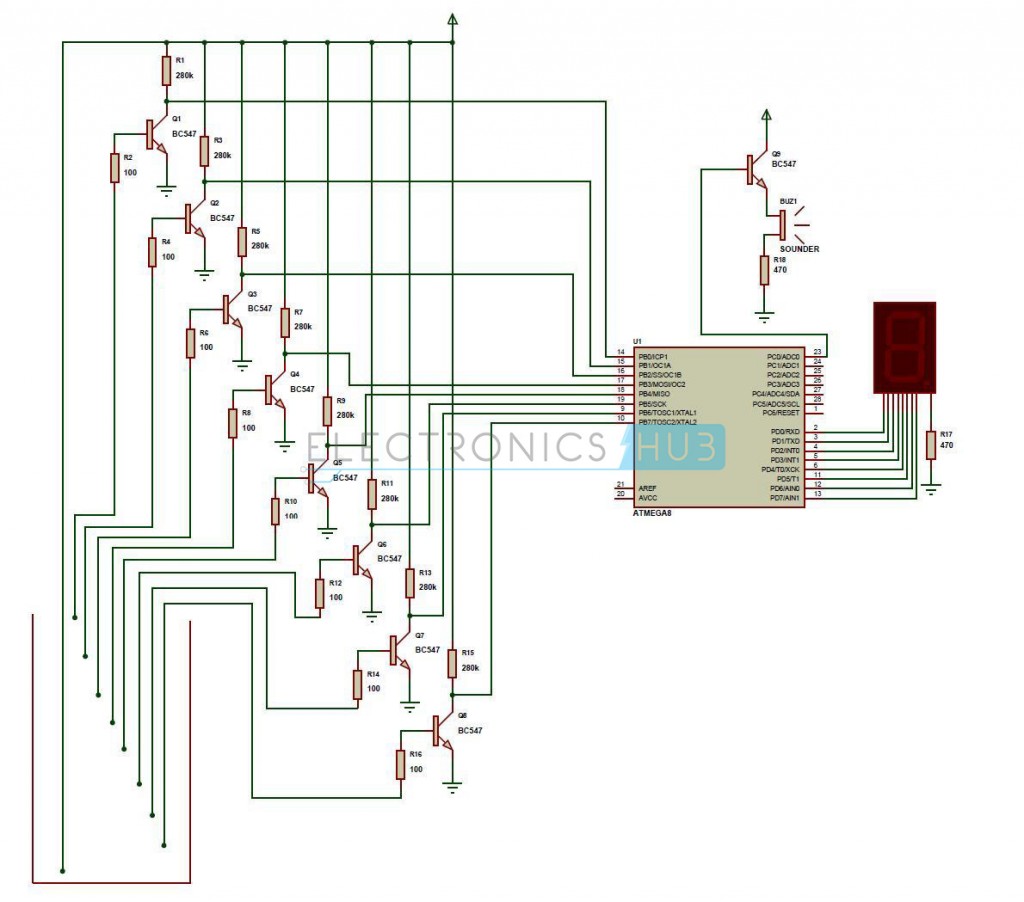

圖6是RAM掉電保護的電路的實例。當電源電壓下降到4.5 V時,4046的開關斷開,RAM的片選信號上拉至"1",RAM中的數據不被沖失;當電源繼續下降至3.6 V時,由蓄電池給RAM供電。

3 結 語

實踐表明,上述抑制電源瞬時波動的措施非常有效,特別是在不用交流穩壓器和UPS的情況下,只利用系統本身功能消除電源波動干擾的方法得到了廣泛應用,大大提高了微機系統的抗干擾能力。

評論