增強電源設計中PFC段性能的方法

大多數的現代電源都要求從輸入線路所吸收的電流包含諧波含量。實際上,規范標準要求線路電流接近正弦波形,而且相位與線路電壓同相。為此,通常在橋電路與大電容之間插入所謂的PFC預穩壓器。這個中間段設計輸出恒定的直流電壓,同時從輸入線路吸收正弦電流。PFC段通常采用升壓配置,要求輸出電壓比線路可能最高的電壓電平都要高。這就是為什么歐洲或是通用主電源輸入條件下輸出穩壓電平普遍設定在約390V的原因。

對于較低功率的應用而言,臨界導電模式(CrM)(也稱作邊界、邊界線甚至是瞬態導電模式)通常是首選的控制技術。這種控制技術簡單,市場上有采用這種技術的不同的商用控制器,容易設計。然而,高輸入電壓時,如果輸入和輸出電壓之間的差距小,PFC段會變得不穩定。本文將說明解決這種問題的方法。PFC段一個更加常見的問題是通常發生在啟動時的大電流過沖,而不論采用的是何種控制技術。

臨界導電模式工作

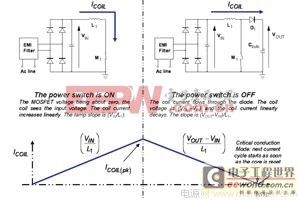

臨界導電模式(CrM)工作是低功率應用中最常見的解決方案。這種控制方法可以采用可變頻率控制原理來描述特征,即電感電流先上升至所需線路電流的2倍,然后下降至零,接著再上升至正電流,期間沒有死區時間(dead-time),如圖1所示。這種控制方法需要電路精確地檢測電感的磁芯復位。

圖1 臨界導電模式工作

零電流檢測

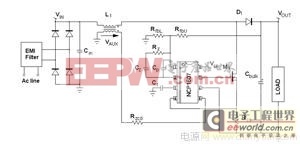

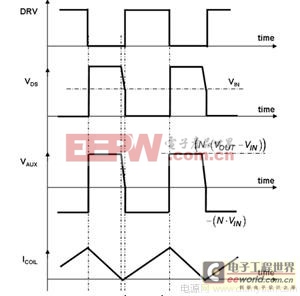

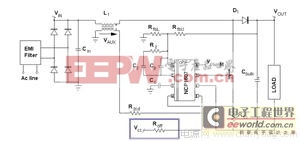

確定退磁完成的常見解決方案在于感測電感電壓,更具體地說,就是檢測電感電壓何時降至零。監測線圈電壓并非經濟的解決方案。相反,這升壓電感與小型繞組相關,這繞組(稱作“零電壓檢測器”或ZCD繞組)提供了電感電壓的一個縮小版本,能夠用于控制器上,如圖2所示。ZCD繞組采用耦合形式,因而它在MOSFET導電時間(反激配置)期間呈現出負電壓,如圖3中所示。這繞組提供:

VAUX=-NVIN,當MOSFET導通時;

VAUX=N(VOUT-VIN),當MOSFET開路時。

其中,N是輔助繞組與主繞組之間的匝數比。

圖2 NCP1607驅動的應用段典型應用示意圖

當ZCD電壓(VAUX)開始下降時線圈電流會達到零。許多CrM控制器內部比較VAUX與接近0V的ZCD參考電壓,檢測出下降沿,并準時啟動下一個驅動信號。為了實現強固的工作,應用了磁滯機制,并實際上產生較高的(upper)閾值(VAUX上升時有效)及較低的(lower)閾值(VAUX下降時有效)。出于不同原因(如安森美半導體NCP1607 PFC控制器中的ZCD引腳的多功能性),在大多數商用器件中這些閾值都相對較高(在1V及2V之間)。

例如,NCP1607數據表中可以發現下述的ZCD閾值規范(引腳5是監測ZCD信號的電路)。

Vpin5上升:最低值為2.1V,典型值為2.3V,最大值為2.5V;

Vpin5下降:最低值為1.5V,典型值為1.6V,最大值為1.8V。

要恰當地檢測零電流,VAUX信號必須高于較高的閾值。

圖3 波形

極高輸入線路時的不精確零電流檢測

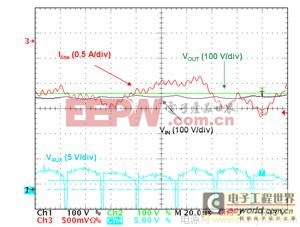

圖4及圖5顯示出在高線路時會面對的一個問題。VAUX電壓在退磁相位期間較小,而這時Vin較高,因為VAUX與輸出輸入電壓差成正比VAUX=N(VOUT-VIN)。此外,如圖4所示,輸入電壓在開關頻率呈現出交流含量。因此,VAUX波形并不平坦,相反,它還包含紋波。在低線路時,這紋波可以忽略不計。在高線路時,VAUX幅度在退磁相位期間較小。因此,這些振蕩可能大到足以導致過早檢測電感磁芯復位。事實上,如圖4和圖5所示的那樣,零電流檢測的精度降低了。

圖4 不精確零電流檢測導致的不穩定性

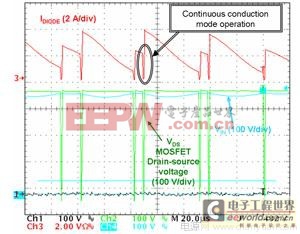

圖5 連續導電模式工作

圖4顯示出現不穩定性問題時高輸入線路(正弦波頂端,此處Vin約為380V)下的VAUX電壓。我們可以看到MOSFET關閉時,VAUX電壓輕微躍升至高于ZCD閾值。由于其大紋波的緣故,在退磁相位期間,VAUX電壓首先增加,然后下降。由于在某些開關周期的末段VAUX接近ZCD閾值,這VAUX電壓下降導致零電壓比較器在電感磁芯完全復位前就翻轉(trip)。圖5證實了這一論斷。有時,升壓二極管仍在導電時,PFC段開始新的周期。這個現象主要導致線路電流失真(見紅色跡線)、功率因數退化,并可能有一些頻率處在人耳可聽到的噪聲。

改善高線路工作的簡單調整方法

如圖6所示,在VCC與引腳5(ZCD引腳)之間布設一顆電阻,能夠減輕或抑制這個現象。這樣一來,ZCD引腳上就產生了偏置。

圖6 ZCD引腳上的調整

在測試的應用中,VCC為15V,且Rzcd=68kΩ。在VCC與引腳5之間增加一顆電阻Roff=680kΩ,就改變了施加在引腳5(ZCD引腳)上的電壓。退磁相位期間ZCD引腳上施加的實際VAUX電壓就變為:

![]() (1)

(1)

然后,施加在引腳5上的電壓就偏置。事實上,這就像是VAUX電壓與減小了1.36V的ZCD閾值比較。這樣一來,新的實際ZCD閾值就是:

Vpin5上升:最低值為0.74V,典型值為0.94V,最大值為1.14V;

Vpin5下降:最低值為0.14V,典型值為0.24V,最大值為0.44V。

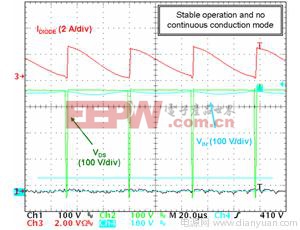

這些降低的ZCD閾值增加了ZCD的精度,并能抑制CCM工作,在相同條件下獲得的波特圖(見圖7)就證實了這一點。

圖7 調整改善器件工作

必須注意,Vpin5下降(我們的案例中是1.5V)時,偏置必須保持在低于ZCD最低閾值。這是為了確保新的實際ZCD閾值(Vpin5下降時) 保持高于0V。否則,系統可能難于檢測磁芯復位并因此啟動新的開關序列。出于這個目的,應當考慮到VCC的變化。

啟動時的大過沖

PFC段從輸入線路正弦波電壓源吸收正弦電流,因此,它們為負載提供僅匹配平均需求的方波正弦功率。輸出電容(大電容)“吸收”實際提供的功率與負載消耗的功率之差值。

● 饋送給負載的功率低于需求時,輸出電容放電,補償功率差額。

● 提供的功率超過負載功耗時,輸出電容充電,存儲多余的能量。

因此,輸出電壓呈現出輸入線路頻率2倍的低頻交流含量。不利的是,PFC電流整形(current-shaping)方法均基于控制信號無紋波的假設。否則,就不能夠優化功率因數,因為輸入線路電流重新復制了控制信號失真。這就是眾所周知的PFC電路動態性能差的原因。它們的穩壓環路帶寬設得極低,從而抑制100Hz或120Hz紋波,否則輸出電壓就會注入這紋波。

由于系統極慢,PFC段遭受陡峭的負載或輸入電壓變化時,會在大電容上呈現出大的過沖

評論