EPS節能方案

對成不同的組合,調節時便根據實際需要挑選最適用的電壓/頻率組合。己可提供多款電源管理集成電路PMIC,其中包括可支持DVS模式的LP3906、LP3907,以及可支持DVS和AVS兩種模式的LP5550、P5551及LP5552。動態電壓調節(DVS)技術可以節省耗電及能源,還為供電電壓預留一些額外的空間,以支持不同上藝及溫度的系統,這個預留的額外中間雖然足以應付最環的情況,但實際應用時便會浪費較多耗電。我們只要關閉系統的電源供應環路,控制環路便可靈活調節操作電壓,并將之降至最低,以便盡量節省能源。PowerWise技術便是利用這個方法節能。

3.2 PowerWise特征

PowerWise接口(PW)可以支持智能的能源管理系統PowerWise是一種針對系統整體需要的能源管理技術,確保以電池供電的電子產品可利用自適應電壓調節(AVS)技術以及控制不同狀態的切換。PowerWise技術采用閉環AVS系統搭配高速的串行電源管理總線,確保處理器無論在任何時候,以任何頻率操作,都可采用最低的電壓,以便將動態能耗降至最低。

PowcrWise技術也可為處理器的電位阱提供偏壓。由于供電電壓Vdd已調低:以減少動態損耗,晶體管的閾值電壓也必須調低,以確保驅動電壓可以保持在較高的水平,但缺點是漏電與靜態功率損耗會增加。我們只要為電位阱提供反向偏壓,漏電便會減少。此外,以同—供電電壓(Vdd)為例來說,我們也叫為電位阱提供正向偏壓,以提高驅動電壓。

可以支持PowcrWise閉環AVS功能的標準系統配置必須有以下的基本元件:內置于處理器之內的先進電源控制器、設有PWI從屬器的電源管理集成電路,以及將兩者連接一起的雙線PWI串行總線。電源管理集成電路負責為處理器提供個同的電壓,電壓大小則由先進電源控制器內的PWI主控器負責調節,辨法是由主控器將有關的命令傳往PWI從屬器,再由相關的電路進行調節。

先進電源控制揣負責接收主處理脂的命令,為電壓控制過程提供一個不受處理器影響的操作環境,以及實時跟蹤邏輯電路的操作速度。先進電源控制器永遠處于戒備狀態,不斷監測系統的一切參數,例如,系統溫度、負載、瞬態、工藝及其他有關的變動都會受到監測?每當先進電源控制器收到有關頻率即將轉變的消息,便會先行作出研判,以確定若以新頻率操作,系統最少需要多少供電才叫可穩定操作。整個過程由閉環電路負責監控,例如先進電源控制器先將電電調節命令經由PWI接口傳送到PWI從屬器,然后再由伺服裝置將電壓調節到適當的水平。

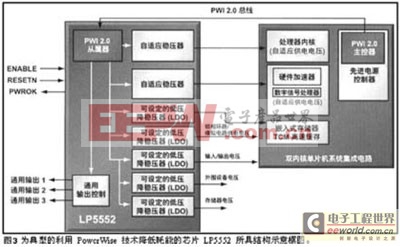

圖3為典型的利用PowcrWise技術降低耗能的芯片LP5552所具結構示意框圖。其技術參數如下。

LP5552輸出數目為7。輸出電壓及電流有:2個降壓穩壓器為0.8v to 1.235v輸出電壓,800mA的輸出電流;5個降壓穩壓器為0.8v to 3.3v輸出電壓,高達250mA的輸出電流。

輸入電壓范圍為2.7V至4.8V。接口為PWl 2.0。封裝為micro SMD-38。

3.3 PowerWise技術應用

PowerWise技術是先進的能源管理解決方案,主要針對當前和未來受能源所限制的數字設備,適用于雙內核處理器、手機、便攜式收音機、個人數字助理、以電池供電的電子產品以及便攜式設備。可將數字處理器的能耗降低70%,從而延長電池壽命、支持更多功能和改善使用者的體驗。PowerWise采用自適應電壓調節(AVS)和閾值電壓調節等技術,將數字邏輯集成電路的工作和泄漏功耗自動降至最低,同時保持最小的系統開銷。

PowerWise技術提供在單芯片系統和支持組件之間的一種優化的閉環回路,而無需CPU干涉。嵌入式PowerWise技術因為可以合成,所以可不受處理器影響。

4 結語

除上述選擇節能芯片和利用利用智能電源管理技術節省能源二個方面之外,需指出的是對于下不同類型的產品其節能技術方式也有所不同。而電源排序技術的應用也是一種較為理想之方案。因為在很多大功率系統中,空間和冷卻系統的成本都很高。因此,就任何POL轉換器而言,做到緊湊、高效率并具有低靜態電流以滿足新的“綠色”標準都是極端重要的。另外,很多微處理器和數字信號處理器(DSP)都需要一個內核電源和一個輸入/輸出(1/( ))電源,這些電源在啟動時必須排序。設計人員必須考慮加電和斷電操作時內核和I/O電壓源的相對電壓和時序,以符合制造商的性能規格要求。沒有恰當的電源排序,就可能出現閉鎖或過大的電流消耗,這有可能導致微處理器I/O端口損壞,或存儲器、可編程邏輯器件(PLD)、現場可編程門陣列(FPGA)、數據轉換器等支持性器件的I/O端口損壞。

評論