節能功耗問題:等離子顯示器降功耗技術

2009年初國內外多家媒體上曾出現關于歐盟要禁售等離子電視的報道。歐盟電視產業研究協會的負責人Paul Gray否認了這一說法,但同時也提到該協會有以下的規劃。

● 將設定平板電視能量效率的最低標準,并且根據屏幕的不同尺寸設定能耗的最大限定值

● 將會強制性要求電視的待機能耗低于1W,這個要求會給生產廠家大約1年的時間來達成

可以看到,盡管歐盟目前并未真正提出要求禁止銷售等離子電視的議案,但是對于該類產品的功耗,包括待機功耗和平均功耗,依然將有明確的限制。這就迫使我們必須花大力就如何降低功耗、提高功率因數、提高發光效率進行不懈地改良和研究。

那么,在哪些方面可以著手進行優化和改善,以有效降低PDP整機的功耗呢?下面我們對此進行定性的分析。

1 電源部分

電源作為PDP的重要組成部分,要求效率高、體積小、能夠提供較大的瞬態輸出功率,并且具有保護功能和不同輸出電壓按順序啟動的功能。

傳統的PDP電源一般采用兩級方案,即功率因數校正(PFC)級+DC/DC變換的電路拓撲結構。它們分別有各自的開關器件和控制電路。盡管其能夠獲得很好的性能,但體積過大,成本高,電路比較復雜。因此,對其進行優化改造也成了PDP電源技術研究的一個方向。

分析可知,不管從傳輸能量角度還是從所占體積的角度,PFC模塊和掃描驅動電極DC/DC變換模塊都占有相當大的比例。因此,對這兩部分的改造就成為PDP開關電源優化改造的一個切入點。

目前的優化方案有以下兩種。

● 單級功率因數校正電路(SSPFC)

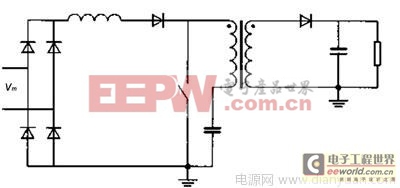

如圖1所示,SSPFC體積小、電路簡單的特點使其成為PDP開關電源小型化改造的一個首選方案。其基本原理是:采用單級功率因數校正變換器電路拓撲結構,單相交流電經全波整流后,通過串聯兩個感性ICS接到雙管反激的DC/DC變換單元。在半個工頻周期內,只有一部分時間電感LB的電流連續工作,當輸入電壓為交流正弦波時,其輸入電流為一含有高頻紋波的近似正弦波。兩者相位基本相同,從而提高了輸入端的功率因數。

圖1 單級功率因數校正電路

● 采用功率因數控制芯片

如圖2所示,可采用MC34262等功率因數控制芯片來進行有源功率因數校正。

圖2 采用MC34262的功率因數校正電路

交流市電經過全波整流后的直流電壓經分壓,輸入控制芯片內乘法器的一個輸入端,而誤差放大器輸出電壓加到乘法器另一個輸入端。在較大動態范圍內,乘法器的傳輸曲線為線性。乘法器輸出電壓控制電流取樣比較器的門限電壓,當電壓大于此門限電壓時,電感釋放能量。此門限電壓近似與輸入電壓成正比,即與交流市電經過全波整流后的直流電壓近似成正比關系。當電感中電流降為零,此時電感開始儲能。其平均電流呈現與市電電壓同相位的正弦波,可使得功率因數接近于“1”。

2 驅動電路部分

在PDP的總功耗中,并非只有氣體放電功耗,因為在PDP的驅動電路中,需要大功率、高頻開關電路來為PDP提供氣體放電所需要的各種高壓脈沖,雖然PDP顯示屏的寄生電容并不消耗能量,但是它們的充電與放電將導致在電路的電阻及電極引線電阻中的能量耗損。

PDP驅動電路的電壓幅值為負幾十伏到正幾百伏左右,工作頻率100~233kHz,驅動電路的設計選型對PDP整機系統的畫面質量、工作效率等尤為重要。

在PDP的驅動電路中,尋址驅動電路的頻率最高,因此,除了在尋址驅動電路中使用能量恢復技術之外,降低尋址驅動電路的脈沖電壓也可以顯著降低尋址功耗。降低尋址電壓脈沖可采用以下幾種方法。

● AwD方法——即“尋址的同時顯示”。尋址、維持、擦除脈沖組合在一起施加,可降低尋址電壓,從而降低無用功耗。同時,由于維持時間占據了一個子場的大部分時間,故維持脈沖的頻率可以降低。

● 擦除尋址方法——即初始化后即進入維持發光階段,待灰度等級到達要求后,通過擦除尋址使這些單元熄滅。因此,每場中單個像素的尋址只有一次。而且,可以用較低的擦除電壓和電流,有效地降低尋址功耗。

● 改變脈沖電路的工作方式——即使開關元件盡量工作在開關管電壓或電流接近零時開通或關斷(ZVS或ZCS)狀態,可降低器件本身的開關損耗。

在大尺寸的PDP顯示屏中,行、列驅動IC的耗用量很多。其功耗大致分為三部分:邏輯部分、電平移位寄存器和高壓驅動部分。正常情況下,邏輯部分功耗在20mW以下,電平移位寄存器部分在200mW以下,因屏電容部分的充放電而產生的高壓驅動電路的無效功耗主要來自于回路中的寄生負載——電阻分量的損耗。這種電阻分量的存在是不可避免的,但對于電容充放電的電能,驅動IC可以通過內置能量回收電路的方式設法回收一部分。

為了滿足高壓器件工作性能的需求,降低高壓驅動部分的無用功耗,PDP驅動IC在設計和工藝上需采取如下比普通的集成電路更為嚴格的控制措施。

● 采用SOI工藝結構,與常規功率模塊相比能量損耗可大大降低

● 采用介質隔離,使驅動IC內部的輸出嵌位二極管可避免串擾現象

● 對于內部元器件結構和布局等給予特殊地處理,利用內部控制可消除高壓開關時的穿透電流

3 MOS管的選型

選擇參數合適的功率場效應晶體管(MOSFET)可使驅動電路能夠高效率、穩定地工作,且壽命滿足要求。要求MOSFET的過渡要足夠快,以便減少開關損耗;導通電阻足夠小,以便減少導通損耗;關斷電阻足夠大,以便提高隔離作用。

其中,漏源導通電阻Rds(on)、反向恢復時間trr、輸入電容Ciss和柵極總電荷Qg需認真考慮。低的導通電阻有助于減少導通損耗,特別是與“能量回收電路”相關的MOS管,低的導通電阻有助于提高能量回收的效率,降低PDP的功耗。trr、Ciss、Qg影響MOSFET的開關速度,低的參數值能夠加快MOSFET的轉換過程,有助于減少MOSFET的開關損耗。另外,低的Ciss和Qg參數,能夠減少MOSFET柵極的驅動功率,簡化柵極驅動電路的設計。

柵極驅動電路是影響MOS管開關損耗的外界因素,優良的柵極驅動電路與高性能的MOSFET相結合,才能制作出高性能的PDP驅動電路。

4 熒光粉材料

PDP用熒光粉和熒光燈用熒光粉非常相似,PDP主要使用的熒光粉有Y2O3∶Eu紅粉、(Gd,Y)BO3∶Eu紅粉、Zn2SiO4∶Mn和BaAl12O19∶Mn綠粉以及BaMgAl14O23∶Eu和MgBaAl10O17∶Eu藍粉。(Gd,Y)BO3∶Eu粉和BaAl12O19∶Mn粉的衰減時間偏長,Zn2SiO4∶Mn的衰減時間對實際應用而言就更長了,因此需研究開發新的發光材料。熒光粉材料直接影響著PDP電視的發光效率和整機壽命。通常等離子電視的壽命指標是指亮度降到一半時的時間。目前新一代長壽命、高亮度的PDP專用熒光粉已經實現商品化。

5 電極結構

通過增加電極間隙來提高PDP的亮度和發光效率是一項非常有效的措施,但電極間隙增大,所需的工作電壓會隨之提高。為解決這一問題,可在維持和掃描電極(X電極和Y電極)中間增加一個浮動電極F。浮動電極在單元工作期間不加電壓信號,但在單個維持電壓脈沖期間,其上會產生一定的感應電勢。由于F電極與其兩側的X、Y電極的間距很小,因而在這兩個間隙處容易首先產生放電。在它們的導引作用下,引起X、Y之間的長間隙放電,從而可降低PDP所需的維持電壓。

6 其他

包括邏輯控制部分、主芯板等,都需要充分考慮降低無用功耗的問題,例如,可以在邏輯控制部分采用門控時鐘的方式,待機狀態下關閉一切內部寄存器的動作,以此達到消除無用功耗的目的。

綜合以上分析,可以看到,降低PDP功耗可以從多個角度考慮,正確的做法是多管齊下,齊頭并進,從電源、驅動方式、熒光粉材料、放電室結構和新型高壓工藝等多方面著手,以求達到最大程度的效率提高。

評論