基于DDS理論的多模式多波形雷達(dá)信號(hào)源設(shè)計(jì)

DDS控制模塊負(fù)責(zé)讀取片內(nèi)雙口RAM中的DDS控制字,并將AD9854的時(shí)序?qū)懭?a class="contentlabel" href="http://www.104case.com/news/listbylabel/label/DDS">DDS芯片,控制DDS的工作。

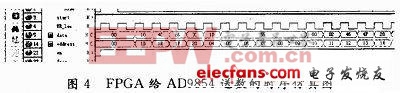

DDS控制模塊在每次寫(xiě)AD9854控制字之前先對(duì)RAM發(fā)出讀使能,同時(shí)給出讀地址,讀取當(dāng)前控制字,然后按照時(shí)序要求寫(xiě)入DDS芯片。Quartus中仿真的時(shí)序圖如圖4所示。

以下將介紹控制AD9854,的流程。

首先對(duì)AD9854進(jìn)行復(fù)位,F(xiàn)PGA發(fā)送高電平給AD9854第71管腳,高電平持續(xù)的時(shí)間長(zhǎng)度要超過(guò)20個(gè)周期的AD9854采樣時(shí)鐘。復(fù)位信號(hào)使AD9854的所有寄存器恢復(fù)到默認(rèn)狀態(tài)。需要注意的是,復(fù)位信號(hào)的長(zhǎng)度必須滿足一定的要求,否則在實(shí)際操作中可能會(huì)出現(xiàn)錯(cuò)誤。

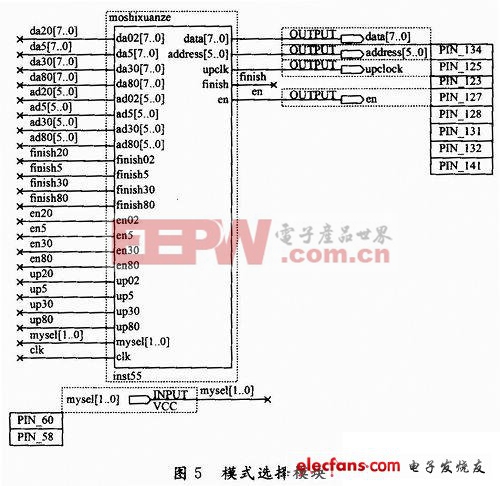

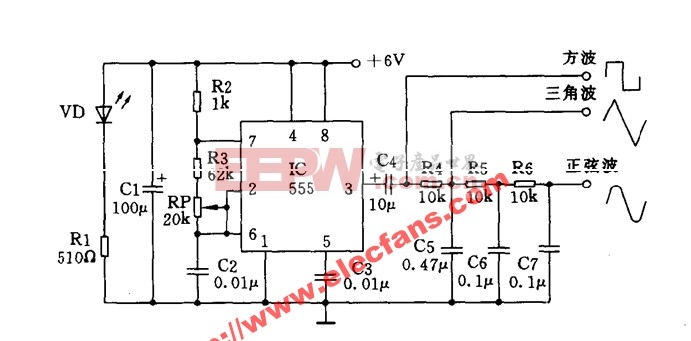

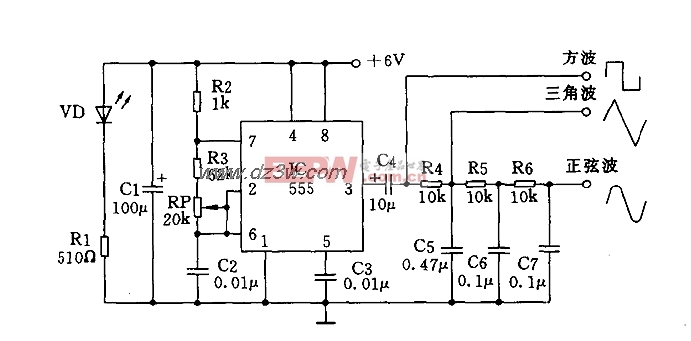

當(dāng)FPGA接收到外部發(fā)送的觸發(fā)信號(hào)以后,DDS控制模塊就開(kāi)始工作了。首先從雙口RAM中讀取波形數(shù)據(jù),包括起始頻率(FTW),增量頻率字(DFW),斜率時(shí)鐘(RRC)以及控制信號(hào)。DDS控制模塊給雙口RAM送讀使能和讀地址,然后把雙口RAM中的數(shù)據(jù)讀到數(shù)據(jù)選擇模塊中。之后接收波形模式選擇信號(hào)。這個(gè)信號(hào)是三位二進(jìn)制數(shù),總共有8種工作模式,總的來(lái)說(shuō)分為工作模式和測(cè)試模式。當(dāng)系統(tǒng)為工作模式的時(shí)候,該系統(tǒng)就是雷達(dá)發(fā)射機(jī)的中頻信號(hào)模塊。在工作模式下,該中頻信號(hào)模塊能發(fā)射4種模式的波形:時(shí)寬是0.2μs的正弦波,時(shí)寬為5μs的線性調(diào)頻波,時(shí)寬為30μs的線性調(diào)頻波和時(shí)寬80μs的線性調(diào)頻波。當(dāng)發(fā)射信號(hào)為時(shí)寬是0.2μs的正弦波或時(shí)寬為5μs的線性調(diào)頻波時(shí),對(duì)近區(qū)的目標(biāo)進(jìn)行搜索;當(dāng)發(fā)射信號(hào)是時(shí)寬為30μs的線性調(diào)頻波時(shí),對(duì)中區(qū)的目標(biāo)進(jìn)行搜索;當(dāng)發(fā)射信號(hào)為時(shí)寬為80μs的線性調(diào)頻波時(shí),對(duì)遠(yuǎn)區(qū)的目標(biāo)進(jìn)行搜索。當(dāng)系統(tǒng)為測(cè)試模式的時(shí)候,也分為時(shí)寬為0.2μs,5μs,30μs,80μs這4種模式的信號(hào),但是當(dāng)信號(hào)時(shí)寬為0.2μs時(shí),信號(hào)中加入了多普勒頻率,這樣就為信號(hào)處理機(jī)檢測(cè)測(cè)速單元提供了方便。該系統(tǒng)為測(cè)試模式時(shí)主要且模擬雷達(dá)回波信號(hào)的作用。如圖5所示。

當(dāng)接收到模式選擇信號(hào)以后,DDS控制模塊開(kāi)始給AD9854送數(shù)據(jù)。這時(shí),F(xiàn)PGA給AD9854傳送的數(shù)據(jù)都保存在I/O緩存區(qū)內(nèi)。接著,F(xiàn)PGA就給AD9854發(fā)送update clock。這樣,I/O緩存區(qū)內(nèi)的數(shù)據(jù)就送入AD9854的寄存器中,AD9854開(kāi)始產(chǎn)生信號(hào)。最后,給AD9854的控制寄存器地址為1F的第七位送高電平,這樣就把信號(hào)清零,從而產(chǎn)生了脈沖信號(hào)。

5 系統(tǒng)測(cè)試

5.1 系統(tǒng)測(cè)試框圖

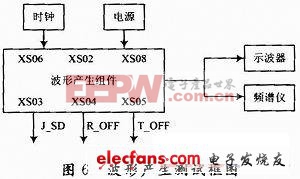

根據(jù)該設(shè)計(jì)系統(tǒng)的設(shè)計(jì)思想和工作原理,結(jié)合系統(tǒng)測(cè)試指標(biāo)要求,提出系統(tǒng)測(cè)試方案和使用儀器。測(cè)試儀表主要包括信號(hào)源、頻譜儀、萬(wàn)用表、電源、示波器等。

按照框圖連接測(cè)試儀表,設(shè)置直流電源輸出電壓為±5 V,通過(guò)相應(yīng)接口送入雷達(dá)信號(hào)產(chǎn)生器的電源接口。設(shè)置信號(hào)源,輸出中心頻率為30 MHz,功率為(0±1)dBm線性調(diào)頻波。測(cè)試時(shí)雷達(dá)信號(hào)產(chǎn)生器工作于外觸發(fā)模式下,當(dāng)接收到外部觸發(fā)信號(hào)時(shí)開(kāi)始產(chǎn)生波形。雷達(dá)信號(hào)源的信號(hào)送入示波器(泰克的DPO4104),測(cè)試信號(hào)的時(shí)域參數(shù),包括時(shí)寬,幅度,脈沖前后沿,本底噪聲等。雷達(dá)信號(hào)源的信號(hào)送入頻譜儀(羅德與施瓦茨的頻譜儀FSMR)測(cè)試信號(hào)的頻域參數(shù),包括信號(hào)的頻率、帶寬、諧波和帶內(nèi)雜散等。

系統(tǒng)測(cè)試框圖如圖6所示。

5.2 系統(tǒng)測(cè)試結(jié)果

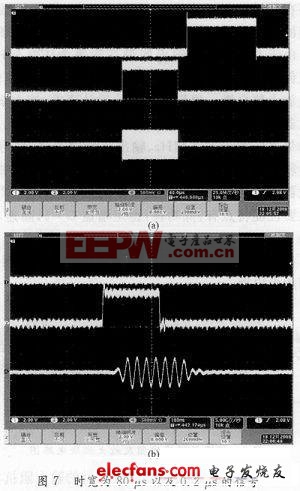

時(shí)域測(cè)試結(jié)果如圖7所示。

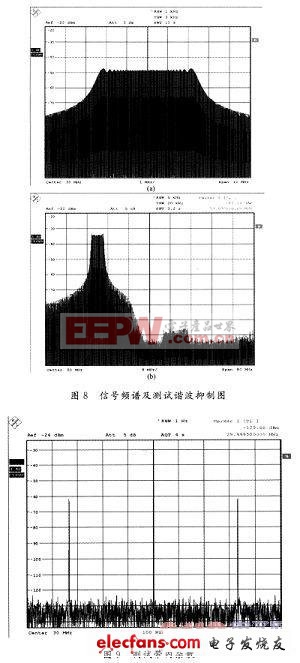

圖8,圖9為頻域測(cè)試結(jié)果。

通過(guò)測(cè)試結(jié)果分析,可見(jiàn)該雷達(dá)信號(hào)產(chǎn)生器系統(tǒng)可產(chǎn)生多種不同時(shí)寬、帶寬和脈沖重復(fù)頻率的LFM、NLFM、脈沖信號(hào),能夠滿足工程應(yīng)用的需要。

6 結(jié)語(yǔ)

評(píng)論