一種高速并行FFT處理器的VLSI結構設計

萬紅星 陳 禾 韓月秋 (北京理工大學 電子工程系信號與信息處理專業,北京 100081)

摘 要:在OFDM系統的實現中,高速FFT處理器是關鍵。在分析了基4按時域抽取快速傅立葉變換(FFT)算法特點的基礎上,研究了一種高性能FFT處理器的硬件結構。此結構能同時從四個并行存儲器中讀取蝶形運算所需的4個操作數,極大地提高了處理速度。此結構控制單元簡單,便于模塊化設計。經硬件驗證,達到設計要求。在系統時鐘為100MHz時,1024點18位復數FFT的計算時間為13µs。

關鍵詞:FFT 蝶形單元 塊浮點 流水線

正交頻分復用OFDM(Orthogonal Frequency Division Multiplex)是近幾年興起的一種在無線信道上實現高速數據傳輸的新技術。它采用多載波調制技術,其最大的特點是傳輸速率高,對碼間干擾和信道選擇性衰落 具有很強的抵抗能力。在OFDM系統中,各子載波的調制解調采用一個實時的快速傅立葉變換(FFT)處理器實現,因此高速FFT處理器是OFDM系統實現中的一個重要因素。目前通用的FFT模塊可以達到的速度數量級為1024點16位字長定點、塊浮點、浮點運算在幾十到數百微秒量級[1],其中采用TI公司的DSP62XX定點系列達到66μs量級處理速度,新近的64XX在600MHz時鐘頻率下完成1024點定點FFT的時間僅需10μs。C6701浮點DSP在167MHz時鐘頻率下完成32位1024點浮點FFT的運算時間需120μs[2]。而AD公司的ADSP-21160 SHARC在100MHz下完成需要90μs。但是如果僅用于FFT處理而廢棄其他功能性價比就很低。采用Xilinx公司的FFT IP核處理,也可以達到160MHz的工作頻率[3],但由于其采用固核,外圍引腳較多不利于使用,且不利于針對特殊要求進行修改。

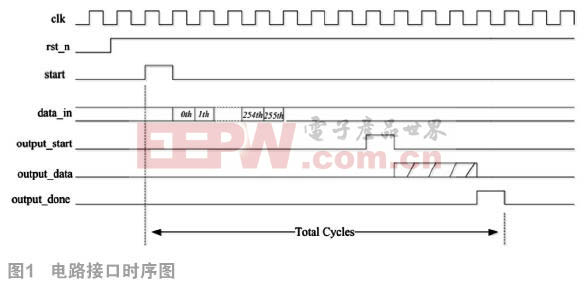

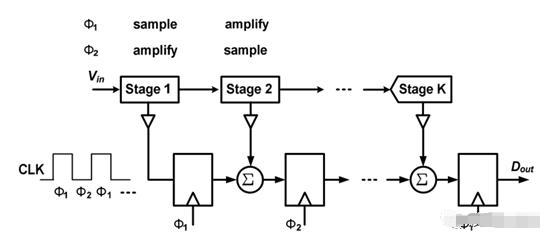

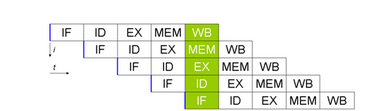

本文在分析了基4按時域分解的FFT算法特點的基礎上[4],提出了一種便于VLSI實現的FFT處理器結構。處理器運算單元的流水并行及操作數的并行讀寫保證了每個周期能夠完成一次蝶形運算。而文獻[5~6]提出的地址映射算法不適用于本設計單蝶形運算結構;文獻[7]中,尋址方案基于線形變換,但是需要復雜的位矩陣點積算法;文獻[8]方案做了改進,但仍然較復雜。本文提出一種完全同址的數據全并行FFT處理器設計方法。此方案僅需要一個計數器,通過簡單的線形變換,即可實現對不同長度N=4p的FFT處理。

1 原理分析

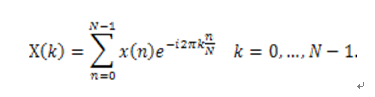

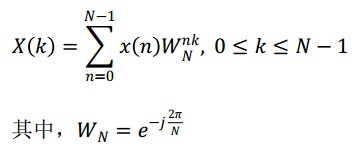

設序列x(n)的長度為N=4p,其中p為正整數,則x(n)的DFT為:

由上述運算步驟可推得基4按時間抽取在第s級的蝶形運算單元的方程為:

其中s為基4 DIT算法流圖中蝶形運算單元的級數;n=b2

評論