反激電源設計之設計控制環路實例

條件: 輸入 85-265V交流,整流后直流100-375V

本文引用地址:http://www.104case.com/article/227251.htm輸出 12V/5A

初級電感量 370uH

初級匝數:40T,次級:5T

次級濾波電容1000uF X 3=3000uF

震蕩三角波幅度。2.5V

開關頻率100K

電流型控制時,取樣電阻取0.33歐姆

下面分電壓型和峰值電流型控制來設計此電源環路。所有設計取樣點在輸出小LC前面。

如果取樣點在小LC后面,由于受LC諧振頻率限制,帶寬不能很高。

1) 電流型控制

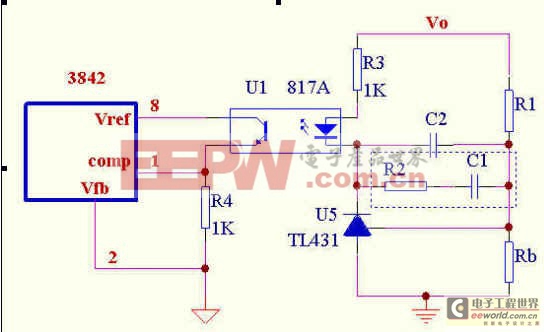

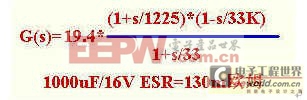

假設用3842,傳遞函數如下

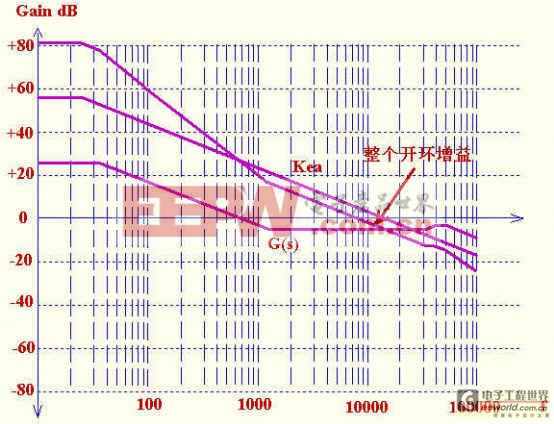

此圖為補償放大部分原理圖。RHZ的頻率為33K,為了避免其引起過多的相移,一般取帶寬為其頻率的1/4-1/5,我們取1/4為8K。

分兩種情況:

A) 輸出電容ESR較大

輸出濾波電容的內阻比較大,自身阻容形成的零點比較低,這樣在8K處的相位滯后比較小。

Phanse angle = arctan(8/1.225)-arctan(8/0.033)-arctan(8/33)= --22度。

另外可看到在8K處增益曲線為水平,所以可以直接用單極點補償,這樣可滿足-20dB/decade的曲線形狀。省掉補償部分的R2,C1。

設Rb為5.1K,則R1=[(12-2.5)/2.5]*Rb=19.4K。

8K處功率部分的增益為 -20* log(1225/33)+20* log19.4 = -5.7dB

因為帶寬8K,即8K處0dB

所以8K處補償放大器增益應為5。7dB, 5.7-20* log( Fo/8)=0

Fo為補償放大器0dB增益頻率

Fo= 1/(2*pi*R1C2)=15.42

C2= 1/(2*pi*R1*15.42)=1/(2*3.14*19.4*15.42)=0.53nF

相位裕度: 180-22-90=68 度

評論