四冗余通信板的仿真 少不了CAN總線技術輔助

隨著電子技術、計算機應用技術和EDA技術的不斷發展,利用FPGA進行數字系統的開發已被廣泛應用于通信、航天、醫療電子、工業控制等領域,FPGA成為當今硬件設計的首選方式之一。PC/104是一種專門為嵌入式控制而定義的工業控制總線,以其獨特的堆棧式結構、低功率等優點,得到了廣泛的應用。作為主流的現場總線,工業控制局域網CAN(Controller Area Network)總線抗干擾能力強,易于組網,具有非常廣闊的應用前景。獨特的PC/104總線與CAN總線的結合,進一步拓寬了CAN總線的應用領域。

本文引用地址:http://www.104case.com/article/226552.htm1 基于FPGA的CAN核設計

本設計采用了Altera公司的Cyclone III系列FPGA EP3C25,開發平臺采用了Altera公司的Quartus II軟件。CAN核的設計以SJA1000功能結構為基礎。

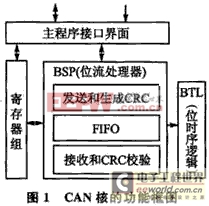

CAN核的功能框圖如圖1所示。該CAN總線控制器IP核,遵循CANbus 2.0標準,其功能和寄存器操作與SJA1000兼容。IP核采用VHDL編碼,并采用容錯設計,可抑制存儲性器件的數據位翻轉,大大提高了IP核的可靠性。CAN核可在FPGA中實現,也可以實現為ASIC。其中包含3個主要模塊:寄存器組(can_registers),位時序邏輯 (can_btl),位流處理器(can_bsp)。

寄存器組(CAN Register):外部微處理器可以通過地址直接訪問這些寄存器。發送數據時,微處理器將要發送的數據寫入發送緩沖器,置位命令寄存器的發送請求位來啟動發送。接收到數據后,核心控制器將其存在接收緩沖器,并通知位控制器將其取走。同時,CAN寄存器中還有1個64字節的接收FIFO,可以1次存儲至少 2個數據幀。

位時序邏輯(BTL):用來監視CAN總線并處理與CAN總線相關的位時序。在消息的開始處,當位時序邏輯檢測到總線上由隱性位(recessive)到顯性位(dominant)的跳變時,就會將其內部邏輯同步到位流,稱之為硬同步;隨后,在接收消息的過程中,檢測到隱性位到顯性位的跳變時,便會重同步到位流,稱之為軟同步。位時序邏輯還要根據總線定時寄存器0和總線定時寄存器1的值來決定每個位周期采樣點的位置,以補償傳輸延遲和相位漂移所造成的誤差;同時,根據總線定時寄存器1的設置采取相應的采樣模式(單次采樣或3次)對總線上的數據采樣。

位流處理器 (BSP):根據其實現的功能分為3個模塊:數據接收模塊、數據發送模塊和錯誤處理模塊。數據接收模塊將從位時序邏輯送過來的采樣數據去除位填充后送到移位寄存器進行串并轉換,之后對并行數據進行CRC校驗,在消息接收完時發送應答信號,表示接收無誤。最后將接收到的消息的特征碼與驗收屏蔽寄存器的內容進行比較,以決定是否將接收的消息寫入接收FIFO。數據接收模塊將要發送的數據組成幀并進行CRC計算,之后送入移位寄存器進行并串轉換,然后將串行數據編碼(位填充)后送到總線上。錯誤監視模塊根據協議規范中描述的錯誤監視機制檢測系統錯誤,并設置相應的寄存器,通知設備控制器。模塊根據協議描述的12 種錯誤監視規則,在適當情況下對計數器進行加、減或清除。控制器根據這兩個計數器的值以及錯誤限制寄存器的值來決定自己的故障狀態:錯誤激活(Error Active),錯誤認可(Error Passire)或總線關閉(Bus off On)。2 硬件電路設計

根據系統的總體設計方案,因為現有的CAN總線收發器最大的工作頻率為1 MHz,在提高CAN的通信速度后,現有的CAN總線收發器就不能滿足需要了,因此改用RS485收發器。由于RS485收發器是差分傳輸,不能完成通信卡的自發自收功能,因此需要外置的CAN Hub。另外,要進行光纖傳輸,要完成光的邏輯總線結構,也需要外置Hub。因此,本硬件設計分為CAN通信板的設計和CAN Hub的設計兩部分。

(1)CAN 通信板硬件電路設計

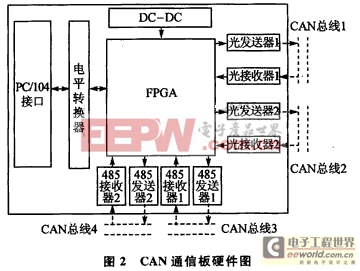

CAN通信板的核心器件是FPGA,同時完成“雙光雙電”通信,硬件通信板結構如圖2所示。

作為PC/104系統的模塊,要接在PC/104總線上,所以要在數據、地址、控制總線上與PC/104標準規定的總線標準一致。

本設計要進行四冗余設計,在設計中要添加4個CAN核,選用Altera公司 Cyclone II系列的FPGA EP3C25。

由于PC/104的工作電壓為5 V,而FPGA的工作電壓為3.3 V,因此在PC/104和FPGA之間要加入1個電平轉換器74LVC245來保護FPGA。

(2)光收發電路

本系統的高速光發射器采用HFBR-1414低功耗高速光發射器件,其光發射波長為820 nm。此發射器能夠與以下4種光纖配合使用:50/125 μm、62.5/125 μm、100/140 μm、200 μm(HCS)。HFBR-1414采用了雙鏡片的光學系統,光發射效率高,當驅動電流為60 mA時,在50/125 μm光纖上可得到-15 dBm的光功率。光接收器采用HFBR-2412,其內部集成了光電二極管、直流電路和開集電極的肖特基晶體管。HFBR-2412光接收器能與光發射器 HFBR-1414及50/125 μm、62.5/125 μm、100/140 μm、200 μm

評論