用雙端口RAM實現與PCI總線接口數據通訊

采用雙端口RAM實現DSP與PCI總線芯片之間的數據交換接口電路。

提出了一種使用CPLD解決雙端口RAM地址譯碼和PCI接口芯片局部總線仲裁的的硬件設計方案,并給出了PCI總線接口芯片寄存器配置實例,介紹了軟件包WinDriver開發設備驅動程序的具體過程。

隨著計算機技術的不斷發展,為滿足外設間以及外設與主機間的高速數據傳輸,Intel公司于1991年提出了PCI總線概念。PCI總線是一種能為主CPU及外設提供高性能數據通訊的總線,其局部總線在33MHz總線時鐘、32位數據通路時,數據傳輸速率最高可達133Mbps。實際應用中,可通過PCI總線實現主機與外部設備的高速數據傳輸,有效解決數據的實時傳輸和存儲問題,為信號的實時處理打下良好基礎。

本文主要提供一種基于PCI總線的數據傳輸系統設計方案,其中雙口RAM起橋梁作用,完成上位機與外圍主控單元之間的數據握手。

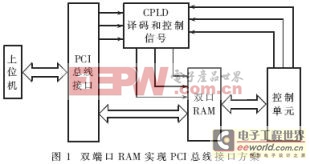

1 雙端口RAM實現PCI總線接口方案

本系統主要用于解決上位機與外圍控制單元的數據傳輸問題。上位機運行信息診斷程序,通過PCI總線與外圍控制單元以一定速率傳輸數據,在主機中實時監控并保存數據。由于實現高速實時數據傳輸,數據量大,所以在PCI局部總線上插入一個高速雙端口RAM。雙端口RAM一端作為PCI總線接口的本地端存儲器,一端作為DSP目標存儲器。需要傳輸保存的數據經DSP處理后借助雙端口RAM和PCI總線接口完成了上位機與DSP的數據握手。本文提出的雙端口RAM實現PCI總線接口方案如圖1。

考慮到PCI總線接口對局部總線的控制時序比較復雜,需要譯碼和控制電路來實現局部總線的訪問及控制。本系統使用CPLD解決雙口RAM的地址訪問競爭沖突問題。需解決的主要問題有:①PCI接口電路設計;②CPLD地址譯碼和總線仲裁;③PCI總線驅動程序開發。

2 PCI接口電路設計

PCI卡的設計一般采用兩種方案。一種是根據PCI協議在FPGA或CPLD中實現PCI總線接口控制器,但是由于PCI協議的復雜性,使得開發難度大、周期長;另一種使用現成的PCI接口芯片,用戶開發難度降低,只把重點放在PCI接口芯片局部總線的接口設計和PCI總線配置空間的初始化,而不用速度考慮PCI總線規范上眾多的協議規范,加快了開發時間。

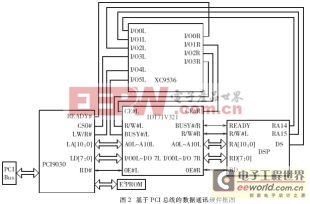

本數據傳輸系統使用PLX公司的PCI9030總線接口芯片,以CPLD完成邏輯控制及與外設的連接,整個系統的硬件框圖如圖2。其中雙端口RAM采用IDT71V321,CPLD選用XILINX公司的XC9536CPLD芯片,EEPROM選用NS公司的93CS56,控制單元DSP選用TMS320LF2407A。

評論