基于FPGA和 C8051F020 的915 MHz射頻讀卡器設計

2.1 讀寫卡操作程序

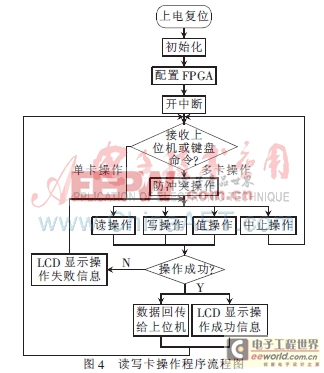

讀寫卡操作程序完成基于ISO/IEC 18000-6 Type B協議的基帶信號編解碼,其程序設計流程圖如圖4所示。

具體工作過程如下:(1)上電復位,系統初始化,包括單片機時鐘、端口、LCD、定時器的初始化,配置FPGA和開中斷。(2)等待接收上位機或鍵盤發送的指令。(3)對指令進行判斷,如果為多卡操作,則進入防沖突子程序;如果為單卡操作,則直接進行讀卡、寫卡、值操作和中止操作。(4)若操作成功,所得數據回傳給上位機,同時驅動LCD顯示操作成功信息;若操作失敗,則驅動LCD顯示操作失敗信息。

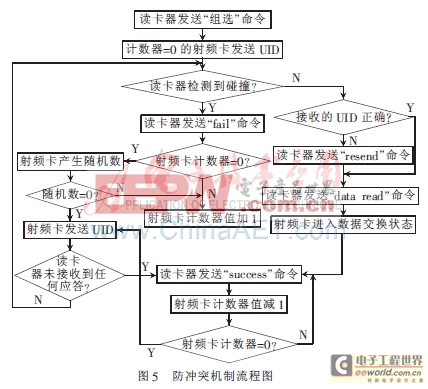

2.2 防沖突程序

當讀卡器對射頻卡進行多卡操作時,在其天線覆蓋范圍內的所有射頻卡將被激活,并處于識別狀態,造成了多張射頻卡讀寫沖突。所以解決沖突是多卡操作的關鍵。ISO/IEC 18000-6 Type B協議詳細規定了防沖突機制,其程序設計流程圖如圖5所示。該防沖突機制的原理是利用隨機產生的0和1信號實現二進制樹形搜索,并且設定了成功命令,進一步提高了搜索的效率,是一種二進制樹形的防沖突算法[7]。具體實現過程為:首先,射頻卡進入讀卡器的工作范圍,從離場掉電狀態進入就緒狀態。讀卡器可以通過GroupSeleet命令和GroupUnseleet命令讓讀卡器工作范圍內處于就緒狀態的所有或部分的射頻卡參與防沖突過程。針對該模式的防沖突機制,射頻卡應該具有如下兩種硬件電路:一個8 bit的計數器和一個0、1隨機數發生器。當射頻卡進入識別狀態(ID狀態)后,將其內部的計數器清0,其中的一部分可以通過接收GroupUnselect命令重新回到就緒狀態,其他處于識別狀態的射頻卡則進入了防沖突執行的過程中。被選中的射頻卡開始下面的循環:(1)所有處于識別狀態并且內部計數器為0的射頻卡將發送其識別碼;(2)如果有一個以上的射頻卡發送識別碼時,讀卡器將檢測到沖突而發送Fail命令;(3)所有接收到Fail命令并且內部計數器不等于0的射頻卡將把本身的計數器加1;所有接收到Fail命令并且內部計數器等于0的射頻卡(即剛剛發送過應答的射頻卡)將產生一個1或0的隨機數。如果選擇了1,射頻卡將把自己的計數器加1;如果選擇了0,射頻卡將保持計數器為0并且再次發送它們的識別碼。在接下來的過程中會出現4種可能的情況;(4)情況1:如果有一個以上的射頻卡發送,將重復步驟(2);(5)情況2:如果所有的射頻卡都隨機選擇了1,讀卡器將接收不到應答,此時,讀卡器將會發送Success命令,所有的射頻卡的計數器減1,然后計數器等于0的射頻卡開始發送,接著重復步驟(2);(6)如果只有一個射頻卡發送并且它的識別碼被讀卡器正確接收,讀卡器將發送包含識別碼的DataRead命令,射頻卡正確接收該條命令后將進入數據交換狀態,開始發送它的數據。此后,讀卡器將發送Success命令,使處于識別狀態的射頻卡的計數器減1;(7)情況3:如果只有一個射頻卡的計數器等于0并且返回應答,重復步驟(5)讀卡器發Success命令或重復步驟(6)發送DataRead命令;如果有一個以上的射頻卡返回應答,重復步驟(2);(8)情況4:如果只有一個射頻卡返回應答,并且它的識別碼未被正確接收,讀卡器將發送一個Resend命令。如果識別碼被正確接收,重復步驟(5)。如果識別碼被重復幾次的接收(這個次數可以基于系統所希望的錯誤處理標準來設定),就假定有一個以上的射頻卡在響應,重復步驟(2)。

經過如上的防沖突過程,射頻場內的射頻卡將可以逐一被識別并進行數據交換。

2.3 串行通信程序

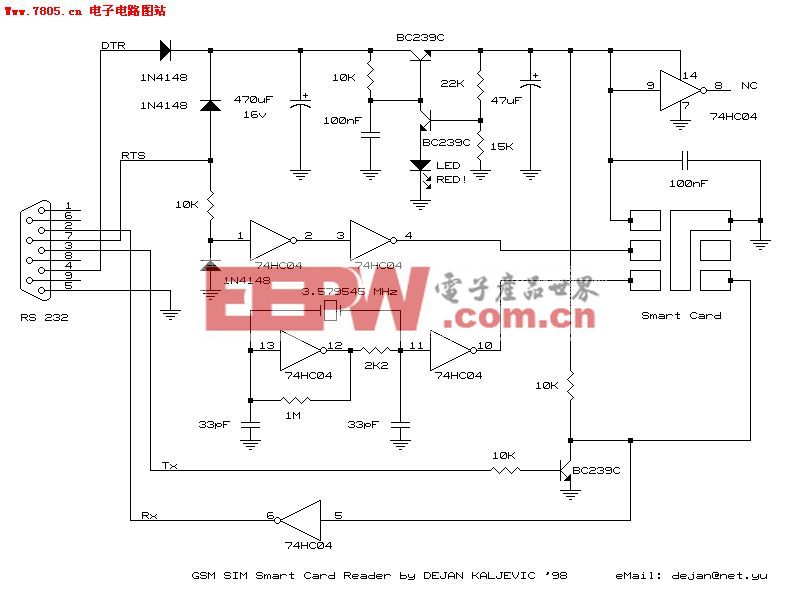

系統使用PC機作為上位機,讀卡器作為下位機。上位機與下位機之間的通信采用基于RS-232-C的串口通信。RS-232-C是一種串行通信總線標準,是數據終端設備(DTE)和數據通信設備(DCE)之間的接口標準,不同廠家生產的設備,只要它們都具有RS-232-C標準接口,則不需要任何轉換電路,就可以互相插接起來。

串行通信程序是MCU與PC機通信的控制程序。發送程序采用查詢的方式設計,即把待發送的數據先送到緩沖區中,然后查詢串口發送中斷標志是不是有空,若有空就發送下一個數據。

接收程序采用中斷的方式設計,即當PC機要發數據給MCU時,主動向MCU申請中斷,接收中斷標志有效,則PC向MCU傳送數據。

3 驗證方案

3.1 驗證平臺的建立

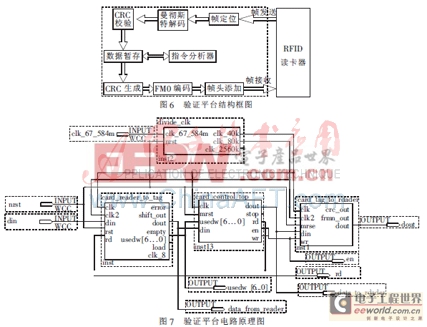

為了驗證所設計的讀卡器能否完成預期的功能,設計了相應的驗證平臺[8]。驗證平臺由數據解碼通道、數據編碼通道以及指令分析器三部分組成。數據解碼通道是對讀卡器發送出的數據幀進行解碼,提取指令的原始數據;指令分析器是對收到的指令數據進行判斷,同時返回相應的數據并發送給數據編碼通道;數據編碼通道則是對發送來的數據進行編碼,再發送給讀卡器。

平臺采用Verilog HDL硬件語言搭建,選用Altera公司Cyclone系列的EP1C6Q240C8芯片為目標器件,使用Quartus II進行綜合驗證,其結構框圖和電路原理圖分別如圖6、圖7所示。

3.2 測試結果分析

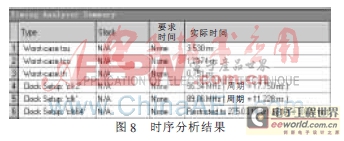

(1)時序分析

通過運行QuartusII 7.1自帶的時序分析器,可以得到時序分析的一些參數:tsu(輸入建立時間)、tco(時鐘到輸出延時)、th(保持時間)分別為3.530 ns、13.174 ns、0.751 ns。基頻時鐘clk最大可以達到89.06 MHz,而ISO/IEC 18000-6 Type B協議規定的基頻時鐘為40 kHz。從分析本系統的時序結果顯示,完全符合協議要求。具體的時序分析結果如圖8所示。

(2)功能分析

功能分析以GROUP_SELECT_LT命令為例。 GROUP_SELECT_LT命令是多卡操作中的組選命令,射頻卡接到此命令,卡內指定地址的數據與幀中提供的數據進行對比。若卡內數據較小,則返回射頻卡的64 bit序列號,否則不作任何響應。GROUP_SELECT_LT命令的命令號為03,地址設為0F,掩碼設為FF,64 bit數據全設為F,所以從MCU傳給FPGA的命令數據為03_0F_FF_FFFF_FFFF_FFFF_FFFF。原始數據經過FPGA數字信號處理模塊處理后,就成了一幀基帶數據信號。驗證平臺將讀卡器發來的數據幀進行解碼,然后判斷指令并返回射頻卡的64 bit序列號,經編碼后成一幀數據幀發送給讀卡器。讀卡器收到此幀后即解碼,并進行CRC校驗,若都沒有錯,則把解碼后的數據傳輸給MCU。

GROUP_SELECT_LT命令仿真波形圖如圖9所示,實驗證明可實現ISO/IEC 18000-6 Type B協議。

隨著RFID相關國際標準的確立(如ISO/IEC 18000)RFID的研發已成為國際性的課題。在諸多RFID工作頻段中,UHF頻段的RFID技術前景最為看好,也成為現今RFID技術領域研究的熱點。

評論