基于FPGA的鐵軌檢測算法設計與研究

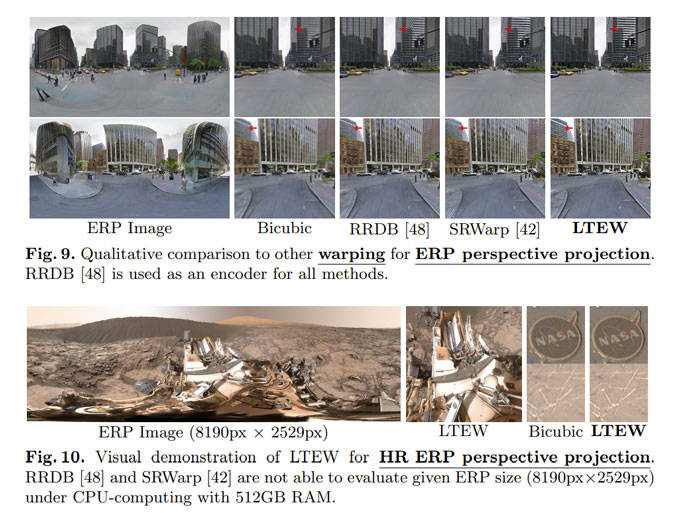

3.2 OpenCV仿真結果

本項目程序首先實現OpenCV仿真,然后移植到FPGA中。OpenCV提供的圖像處理算法非常豐富,并且部分程序以C語言編寫,處理得當,不需要添加新的外部支持就可以完整的編譯連接生成執行程序進行算法移植。本次仿真只運用“cv.h”和“highhui.h”兩個OpenCV庫,主要是運用其圖像加載、圖像顯示等函數,而中值濾波、邊緣檢測、鐵軌搜索函數自行編寫。仿真結果如圖4所示。

3.3 FPGA程序移植過程

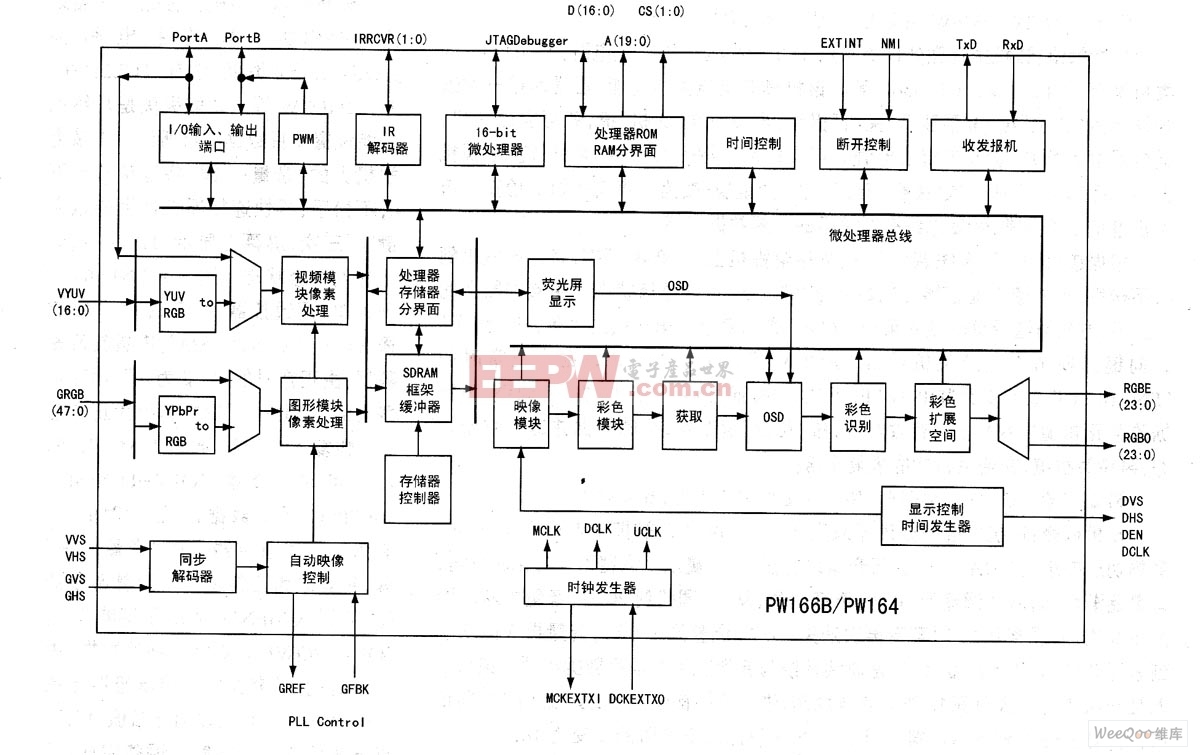

3.3.1 圖像輸入與顯示[3]

本項目把圖像數據轉換為.ELF文件格式,燒錄到NOR-Flash,在XPS的菜單下點擊Program Flash Memory,選擇自動格式轉換,即可進行燒錄,而且可以指定燒錄數據的位置。數據格式轉換利用Matlab軟件完成,程序如下:

fid = fopen(′pic.elf′, ′w′);//打開文件

img =imread(′Image03.BMP′);//讀圖像數據

imshow(img);//顯示圖像

fwrite(fid,img.′);//寫數據

fclose(fid);//關閉文件

由于是灰度圖像,只讀取其亮度值。圖像分辨率為640×480。寫數據可以用fprintf函數或fwrite函數,但是實驗表明使用fprintf函數寫數據,文件大小302 kB,顯示圖像不正常;而使用fwrite函數寫數據文件僅300 kB,顯示圖像正常。說明兩種函數寫數據方式本質不同,造成寫入數據格式不同。

圖像顯示過程:先從Flash中每次一行把數據讀入BRAM,然后把每一位亮度值移位變為R、G、B三位,再從BRAM讀數據到SDRAM顯存,如此循環480次,用以顯示圖片。由于R、G、B值相同,顯示的便是灰度圖像。如果直接從Flash讀數據到SDRAM顯存,顯示圖像每行有不規則不連續的黑點,甚至顯示不正常。顯存的設置在TFT-Controller IP中完成,顯存空間為2 MB,起始地址與SDRAM起始地址相同。

3.3.2 圖像處理程序移植[3]

由于開發環境不同,移植后程序在獨立系統上運行,需要對OpenCV仿真程序做一些改正。FPGA編程系統支持C語言標準庫函數,所以打印輸出顯示函數print()、動態內存分配函數malloc()可以直接使用。盡管printf()函數也可以用于打印輸出結果,但目的是把程序放入大小為32 KB的BRAM,實驗表明它比print()函數占用空間大一倍。在OpenCV中,可以直接使用cvShowImage()、cvReleaseImage()、cvDestroyWindow()函數顯示圖像和釋放內存空間,在移植程序中要自行設計這些函數。移植程序中subplot()函數用于在屏幕上顯示4幅圖像(降低分辨率源圖像、濾波圖像、閾值分割圖像、鐵軌檢測圖像),DeleteAllPointElems()函數用于釋放內存空間。其他函數,例如降低分辨率函數Dec()、濾波函數filter()、邊緣檢測函數edge(),可以完全使用OpenCV中的程序,不需要做修改。移植后主程序如下:

int main()

{ print("rn-- Entering main() --rn");

SourceImage=(Xuint8*)malloc(640×480);

DecImage=(Xuint8*)malloc(320×240);

FilterImage=(Xuint8*)malloc(320×240);

EdgeImage=(Xuint8*)malloc(320×240);

ResultImage3=(Xuint8*)malloc(320×240);

//為圖像分配內存空間

if (SourceImage==NULL)

{print("rn--mem allo fail--rn");

exit(1);}//驗證空間是否分配成功

XTft_Initialize(Tft, TFT_DEVICE_ID);

//TFT顯示初始化

XromTftTestColor("black", 0);

//顯示背景設置為黑色

flbuf=(unsigned char*)Flash_BASEADDR;

//設置Flash圖像基地址指針

p=SourceImage;//設置源圖像指針

for (y=0;yHEIGHT;y++)

{rowpoint1=flbuf+y*WIDTH;

for(x=0;xWIDTH;x++)

{data1=*(rowpoint1+x);

*p++=data1;

} }//讀源圖像數據

dec(SourceImage,DecImage);

filter(DecImage,FilterImage,320);

edge(FilterImage,EdgeImage,320);

//圖像降低分辨率、濾波、邊緣化

nt areanum=0;

GetFeature(EdgeImage,320,240,

ConnLabel,pFeatures,areanum);

//邊緣提取,搜索連通域

GetRailArea(320,240,pFeatures,

areanum,lowLeftRail,lowRightRail);

//搜索鐵軌區域,獲得左右軌

int i, j;

for (i=1; i = areanum;i++){

DeleteAllPointElems(pFeatures[i]);}

//釋放內存空間

int Left,Right;

for(i=1;i240; i++){

Left=lowLeftRail[i];

Right=lowRightRail[i];

if((Left>0)(Right>0)){

for(j=Left;j=Right;j++){

*(TrackImage+i*320+j)=255;}}}

//填充鐵軌左右軌之間區域

subplot(DecImage,1);

subplot(FilterImage,2);

subplot(EdgeImage,3);

subplot(TrackImage,4);

//顯示4幅處理圖像

print("-- Exiting main() --rn");

}

FPGA圖像處理結果如圖5所示。

本文實現基于FPGA的鐵軌檢測算法,首先完成OpenCV程序仿真,然后移植到FPGA構建的硬件系統中,可以成功檢測出鐵軌所在區域,并在一定條件下進行鐵軌智能延長。研究結果表明,檢測一幅分辨率為640×480圖像,大約需要30 s,如果應用于實時視頻流系統中,則硬件平臺設計需要進行精簡,以提高速度。也可考慮基于硬核、多核技術,來提高處理速度,以滿足實時視頻流處理。

評論