FPGA實現視頻廣播接收系統方案

2.FPGA設計

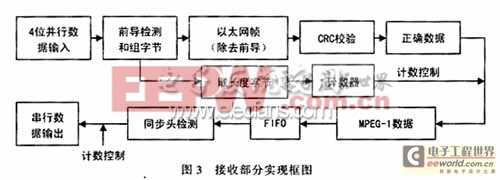

由于要使數據能在以太網上傳輸,服務器端的發送程序應該把要傳輸的數據進行打包(或封裝)。本系統中所要傳輸的數據為視頻數據(VCD數據),而VCD數據一般是以dat格式存放在光盤中的。因而在接收端應對接收到的數據包進行解包,并同時完成數據格式轉換的功能,使得送到MPEG-1解碼芯片的數據格式為dat格式的數據,從而進行解碼,最后用普通的電視機就能夠接收。

因而該部分主要要實現的功能是:先完成對接收到的以太網數據幀進行解包,取出封裝在以太網數據幀中的數據部分,然后再分別解IP數據包和UDP數據包,把真正的具有VCD播放格式的數據取出來,經過一個先進先出(FIFO)緩沖器輸出到MPEG-1解碼芯片進行解碼。其中在解包的過程中,要對數據進行校驗,校驗正確的數據包才進行傳送,對于校驗不正確的數據包采用了直接丟棄的方法,所采用的校驗算法是循環冗余校驗算法(CRC)。

設計框圖如圖3所示。

(1)前導檢測:當系統檢測到連續出現了15個nibble的1010,同時隨后的一個nibble為1011時,說明一個以太網數據幀開始了,應該對該部分的數據作進一步的處理。

(2)組字節:由于從DM9101芯片出來的數據信號是以一次四位元組(nibble)的形式傳輸的,因而要對它進行組字節操作,每2個nibble組成一個字節,具體操作過程依據的是MII幀結構中的字節組成格式進行。

(3)CRC校驗:對以太網幀中的目的地址、源地址、長度、數據進行CRC校驗,并與幀的最后四個字節進行比較,如果一致,即為正確的以太網數據;若不一致,則丟棄這一幀。

(4)MPEG-1數據:取出以太網幀中的長度字節的值,用這個值來預置一個計數器,從而對數據進

行計數控制,取出其中的MPEG-1格式的有效數據。

(5)FIFO:由于普通的以太網的數據傳輸速率是10

Mbps或100 Mbps,而進行MPEG-1解碼時的速率一般為1.5 Mbps左右,因而要對數據流進行速率調整。該FIFO直接利用了Spartan II系列芯片內部的存儲模塊進行緩存。

(6)同步頭檢測:dat格式的數據幀有一個同步頭為:00FFFFFFFFFFFFFFFFFFFF00(十六進制),當檢測到該同步頭時,表明一個dat數據幀開始了,應將其后的數據連同該同步頭信息一起輸出至解碼芯片。

(7)串行輸出:把最后得到的數據轉換為串行數據,并以I2S的格式將數據和時鐘等信號輸出到 MPEG-1解碼芯片中進行解碼。

四、仿真結果

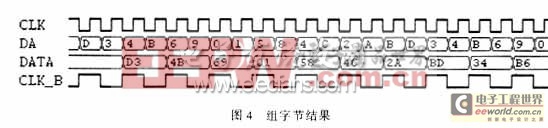

1.組字節仿真結果

數據從2個nibble組成一個字節的仿真結果如圖4所示。其中,CLK信號是25 MHz的時鐘信號,DA是由4位數據組成的數據信號,它們由DM9101芯片輸出;DATA為組成字節后的8位數據信號,CLK—B是由CLK信號二分頻所得到的Byte時鐘信號。

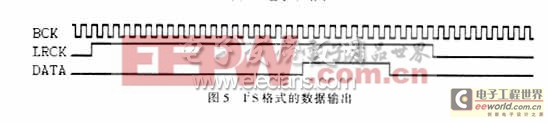

2.I2S格式仿真結果

以I2S格式輸出的數據的仿真結果如圖5所示。仿真中采用的格式是:32位BCK,MSB最先,右通道為低電平。其中BCK是位時鐘信號,LRCK是左右時鐘選擇時鐘,DATA是VCD格式的MPEG-1視/音頻數據。

五、小 結

本系統所采用的FPGA芯片為Xilinx公司的Spartan II系列芯片,用Foundation軟件工具開發。設計輸入完成后,進行整體的編譯和邏輯仿真,然后進行轉換、布局、延時仿真生成配置文件,最后下載至 FPGA器件,實現其硬件功能。由于系統的很多功能由一塊FPGA實現,外圍器件很少,所以系統體積小、可靠性高,且器件的可編程性使得系統功能易于完善。仿真結果表明,各信號的邏輯功能和時序配合完全達到了設計要求。

評論