高效FIR濾波器的設計與仿真-基于FPGA

2 高效FIR濾波器的FPGA實現(xiàn)

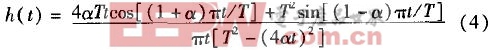

在實際的數(shù)字傳輸系統(tǒng)中,接收端和發(fā)送端為了達到最小的誤碼率,一般采用平方根升余弦濾波器。該濾波器的系統(tǒng)函數(shù)是:

式中:α是滾降系數(shù),0≤α≤1,T為碼元周期。

若取滾降系數(shù)α=1,濾波器長度為31,每個碼元取4個樣點,濾波器的系數(shù)采用10位量化,則可得到平方根升余弦濾波器的系數(shù)為h(n)=

{4,7,2,-7,9,4,22,25,-3,-53,-83,-43,88,277,445,512,445,277,88,-43,-83,-53,-3,25,22,4,-9,-7,2,7,4}。

根據(jù)以上思路,采用Altera公司Cyclone系列的EP1C3T100C6芯片,在Quartuas II開發(fā)軟件下對此FIR濾波器進行設計及仿真。首先利用

VHDL語言完成設計輸入,然后用Compiler進行編譯調(diào)試。編譯通過后,再利用該軟件所提供的Waveform Editor進行時序仿真,得到的時序仿真波形如圖3所示。其中,cP是控制輸入的時鐘信號,時鐘頻率為50 MHz,clr是加法器及鎖存器的清零信號,低電平0有效,X是外部的輸入信號,Y是最終的外部輸出信號。

圖3 FIR濾波器時序仿真圖

用Waveform Editor仿真后,將生成的波形轉(zhuǎn)化為tbl文件,提取出波形數(shù)據(jù)。通過Matlab軟件可以畫出這些數(shù)據(jù)對應的圖形,即濾波結(jié)果圖,如圖4中的虛線所示,圖中橫坐標是采樣點數(shù),縱坐標代表的是采用10位二進制數(shù)量化后的幅值,圖4中的實線是FPGA濾波結(jié)果。從圖4可以看出.用本文提出的設計方案實現(xiàn)的基于FPGA的FIR濾波器的濾波結(jié)果與理想濾波結(jié)果是非常接近的,對比圖中FPGA濾波結(jié)果比理想值稍低,原因是由于在FPGA濾波器實現(xiàn)的過程中,為了節(jié)省硬件資源,將數(shù)據(jù)做了截掉低6位的處理,從而產(chǎn)生了一點誤差。但是,從仿真結(jié)果來看,該截掉低位的處理并不影響濾波器的性能。

圖4 FPGA仿真濾波結(jié)果與理想FIR濾波結(jié)果對比圖

利用軟件所提供的Timing Analyzer進行時間分析,可知此FIR設計方案的信號輸出延遲在6.8 ns左右。即系統(tǒng)的最高工作頻率為147 MHz。

從仿真結(jié)果中還可得到硬件資源的占用情況及利用率情況,實現(xiàn)該FIR濾波器共占用961個邏輯單元,邏輯單元利用率為33% 。

由以上分析可以看出,該設計方案不管是在速度及實時性方面還是在資源利用率上,都具有很大的優(yōu)勢。將其應用至通信系統(tǒng)或信號處理領域中均可滿足實際的需要。

3 結(jié)論

FIR濾波器在數(shù)字信號處理的各個領域中起著舉足輕重的作用,它的性能優(yōu)劣對信號處理的結(jié)果有很大的影響。本文采用對稱結(jié)構(gòu)、加法和移位代替乘法運算、優(yōu)化的CSD編碼、流水線技術(shù)、級聯(lián)技術(shù)幾個方面,對傳統(tǒng)的FIR濾波器的設計進行了改進,并借助Altera公司的FPGA芯片和Quartuas II軟件以及Matlab軟件對設計方案進行了仿真驗證。仿真實驗結(jié)果表明,該FIR濾波器的實現(xiàn)方案,具有工作速度快、實時信號好、節(jié)省硬件資源等特點,能夠滿足實際的數(shù)字系統(tǒng)的要求,應用方便。

評論