高清晰LED顯示控制模型設計分析

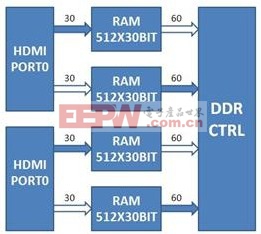

視頻處理器主要完成的功能是視頻分割,視頻流控制,畫中畫,白平衡等常用的視頻處理技術。如圖3所示,視頻處理器配有兩路HDMI輸入接口和四路HDMI輸出接口,采用基于ARM+FPGA的系統架構,配合DDR166SDRAM,并提供OLED和用戶接口,實現良好的人機互動能力,方便用戶使用。視頻處理器接收2路HDMI信號,根據用戶需要,將其融合成為一路HDMI視頻流,并分割為4路XGA格式輸出。

內存的數據吞吐速度是本設計中的一個重點,如果內存速度不夠,將會導致丟幀,反映到大屏幕上就會出現嚴重的抖動,甚至無法顯示等問題。對于任意分辨率的視頻信號,其總帶寬由公式(1)計算得出。

![]()

公式(1)中,P為視頻總像素數量,B為每個像素的色彩深度,R為刷新周期。由公式(1)可以得出1080p@60Hz的視頻信號的總帶寬為:

1,920x1,01 8x30bit=3.8Gbps

DDR166 SDRAM核心工作頻率僅為166Mhz,但由于DDR采用2BIT預讀取技術,每個時鐘周期處理2bit數據,而傳統的SDRAM每周期只處理1bit數據。因此DDRSDRAM比傳統的SDRAM的速度快了將近一倍,其每個I/O數據吞吐速率可達300Mhz。

根據DDRSDRAM的工作原理,可以得到計算DDRSDRAM帶寬的公式(2):

![]()

公式(2)中,B為DDRSDRAM的數據位寬,為核心工作頻率,由公式(2)可計算求出主頻率166Mhz位寬30bit的內存的總帶寬為9.9Gbps。但由于動態內存存在刷新和指令操作,實際帶寬不可能達到這個數值。

對于乒乓操作而言,輸入總帶寬和輸出總帶寬必須滿足下列關系:

![]()

如果和不滿足公式(3)的不等式關系,那么,在實時處理中將會丟失數據包,從而造成大屏幕抖動或不能正常顯示。

在本設計中,由于接入2路HDMI輸入,所以輸入總帶寬為一路的2倍,即7.6 Gbps,顯然,7.6 Gbps的兩倍要遠大于9.9Gbps,因此DDRSDRAM必須擴展其位寬到60bit,從而增加其數據吞吐速率。

高清晰LED顯示控制模型設計分析

2013-03-18 16:49文章來源:電源網有3184人閱讀過

圖4. 乒乓操作

系統輸入端數據處理如圖4所示,兩路HDMI輸入采用乒乓操作,共需要4塊512x30bit的RAM。每塊RAM對于DDR SDRAM為256x60bit。1次向DDR SDRAM中寫入512個像素的數據,可以提高內存的使用效率。

HDMIPORT持續的向RAM中寫入數據,每當寫滿一塊RAM后,發送ACK信號給DDR CTRL模塊,該模塊根據接收到的ACK信號,自動將RAM中的數據分配給DDR SDRAM中的相應區域,如果兩個端口都沒寫完,則將DDR SDRAM中的數據讀出,分配給后端的HDMI發送口。從而實現實時視頻處理的功能。

3.2顯示的層次結構

發送卡的系統模型如圖5所示,采用FPGA作為系統的處理核心,配合SDRAM 166處理1024*768*60hz的視頻信號,并加入千兆以太網模塊,USB轉SPI總線模塊,在為大屏幕傳輸視頻信號的同時,還可以接收上位PC機的矯正系數和控制信息,并將其發送給大屏幕,同時,全雙

相關推薦

-

-

-

-

-

jackwang | 2011-03-07

-

licon | 2007-08-21

-

-

-

-

-

jackwang | 2006-09-17

-

licon | 2007-08-21

-

jianzhangx | 2011-11-15

-

評論