51單片機+CPLD讓系統更高效

三、單片機與CPLD接口設計

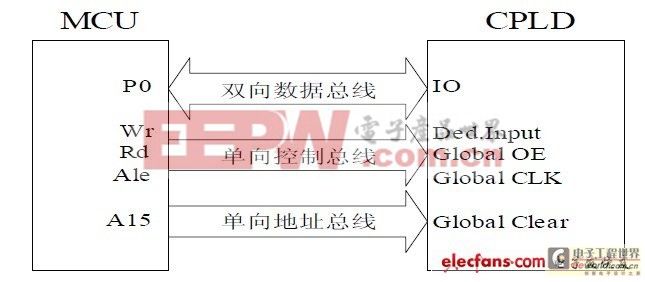

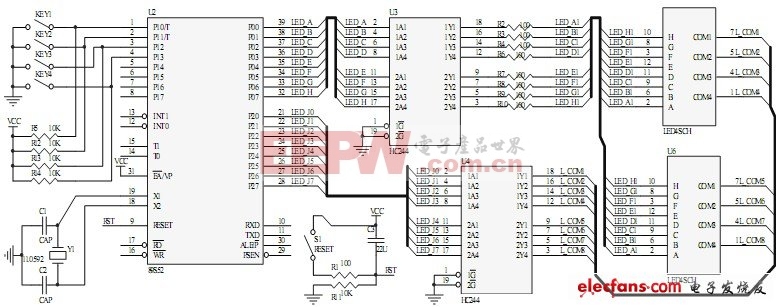

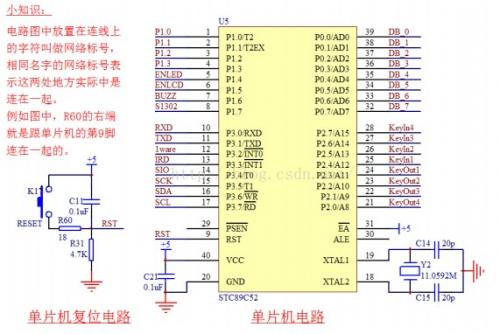

以上經典電路中,系統擴展使用了單片機總線模式,各個對象采用的三總線連接,根據這種電路結構,這里給出一種單片機同CPLD 的總線接口模式,如圖4 所示。

圖4 單片機與CPLD總線接口示意圖

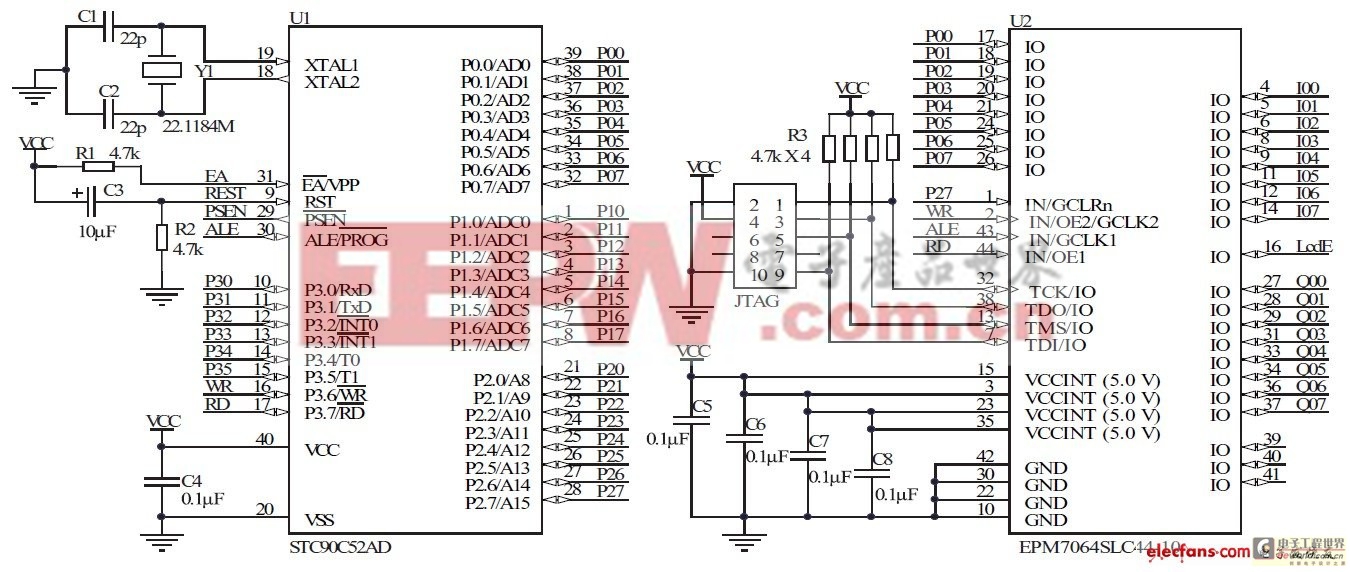

這里選擇A l t e r a 公司早期的EPM7064SLC44-10 為例,這是很老的一款CPLD器件,是5V 供電。其實選擇什么CPLD 型號并不是關鍵,關鍵是學習用CPLD 代替分立器件的思想和方法。數據總線P0 口同CPLD 一般IO 口相連,完成數據和低8 位地址傳送;控制總線包括單片機讀寫控制信號Rd(P3.7) 和Wr(P3.6),以及地址鎖存信號ALE(Address Lock Enable)和高位地址線A15(P2.7) 通過CPLD 的全局信號引腳輸入,包括全局時鐘輸入:INPUT/GCLK1, 全局清零輸入INPUT/GCLRn, 全局使能輸入INPUT/OE1,INPUT/OE2, 這幾個信號有專用連線與CPLD 中每個宏單元相連,保證信號到每個宏單元的延時相同并且延時最短。實際電路原理圖如圖5所示。

圖5 MCU與CPLD接口電路原理圖

這樣一塊CPLD 器件就代替以上除單片機外的7 塊芯片了,在電路板上將節約大片的PCB 面積,好處還遠不止這些,因為CPLD 是二次開發的,其內部電路可以根據需要再次設計,反復修改,極大的增加了電路設計的靈活性。

讀者看到這里,肯定對自己動手設計CPLD 電路充滿了期待,下面介紹如何借助工具軟件開發CPLD 內部電路。

四、CPLD開發介紹

一般來說,CPLD 生產商都有配套的開發工具, 這里介紹ALTERA 公司的一款易學易用的CPLD 開發軟件MaxPlusII,雖然該公司最新版的軟件是QuartusII,但針對某些具體的器件,選擇MaxPlusII 還是很方便的。該軟件入門教程請到百度搜索《MaxplusII 設計CPLD 入門》,很多手把手的資料。

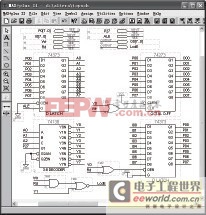

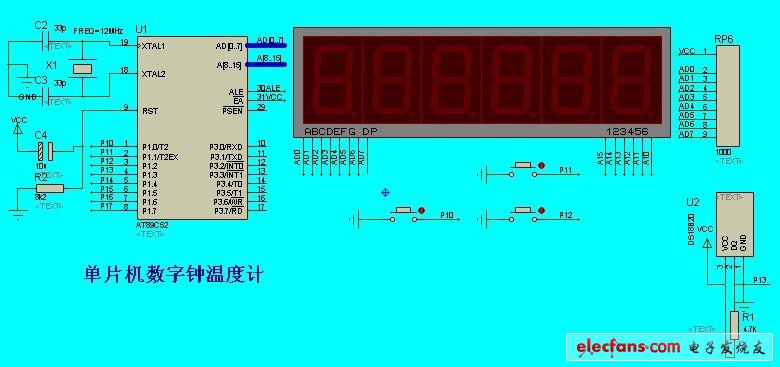

最容易的電路設計方法不外乎是直接繪制電路原理圖。采用原理圖輸入,初學者甚至不需要額外學習就可以從事CPLD 設計。我們只需要在軟件平臺上從集成器件庫調出對應的器件,繪制相同的電路原理圖即可,實現以上功能電路原理圖繪制完成后如圖6 所示。

圖6 原理圖輸入設計CPLD

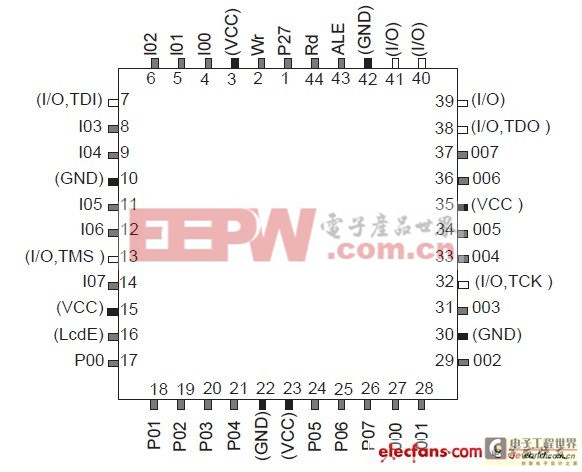

該原理圖編譯成功后,我們還需要根據實際電路連接圖分配綁定引腳,引腳綁定如圖7 所示,再編譯就可以得到可供下載的文件*.pof 了,最后只需要將下載電纜連接到電路板上,仍然通過該軟件即可完成下載。

正因為CPLD 的IO 腳是可以隨意分配的,通常我們會結合實際的PCB 板設計布線的便利來調整引腳分配,引腳分配更改后,只需要重新分配引腳再編譯下載即可。

圖7 CPLD引腳綁定

除了原理圖輸入外,復雜的CPLD 器件開發,一般用硬件描述語言設計,常用的硬件描述語言有VHDL,VerilogHDL,這些硬件描述語言的掌握是需要系統學習的,基于硬件描述語言的片上系統設計,FPGA 開發目前已經成為高薪職業,社會需求巨大。用硬件描述語言開發CPLD 的方法與前面的原理圖輸入法類似,也需要編譯糾錯,時序仿真,引腳綁定,最后編譯下載即可。

給CPLD 下載完程序,這塊芯片就是你所設計的邏輯時序電路了,通常比分離元器件功耗更低,性能更優。

真正是基于上述思想, 筆者將51 單片機同CPLD 相結合,開發了一款適合初學者使用的學習板--Mini51 板。

評論