基于51單片機和FPGA的頻率特性測試儀的設計

2.4 相位測量模塊的方案

該模塊采用相位一時間轉化法。兩個頻率相同、相位不同的正弦信號經整形異或運算后產生脈寬為Tx、周期為T的方波,相位差與(TX/T)之間始終存在一一對應關系。因此無論頻率如何變化,只要測出(Tx/T),相位差的大小也就確定。

3 理論分析與計算

3.1 DDS相關計算

由DDS原理可得:

式中,N為相位累加器位數,K為頻率控制字。

當K=1時,可知DDS的最低輸出頻率為:

此即DDS的頻率分辨率。

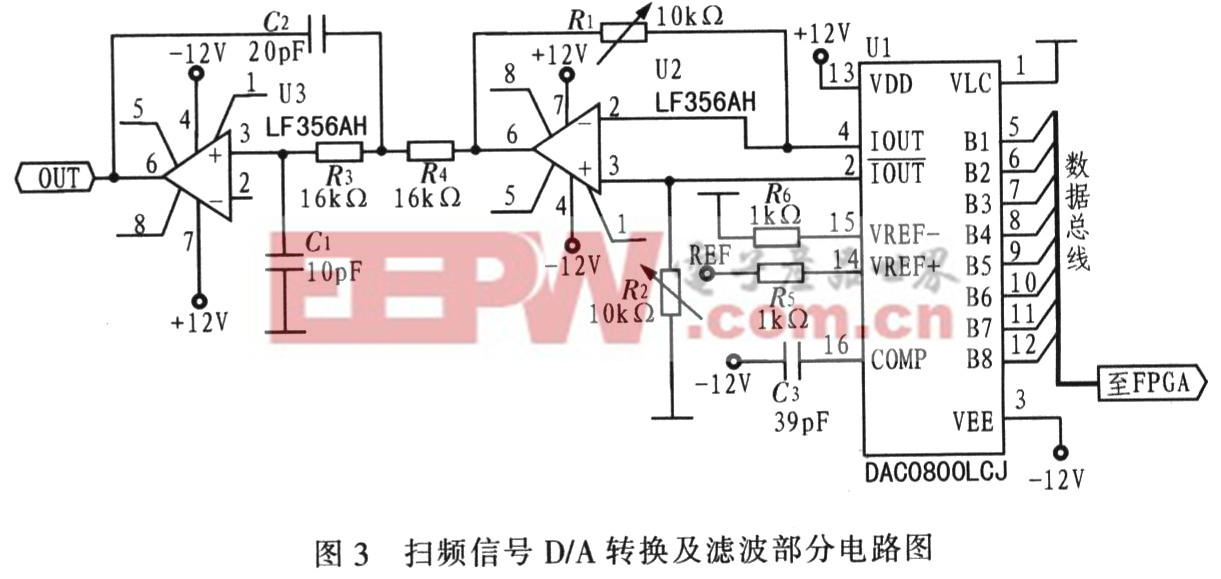

(1)移相信號發生器部分DDS由于輸出級D/A轉換器DAC0800的建立時間為100 ns,則時鐘頻率應小于10 MHz,取時鐘頻率fout=8.388 608 MHz,相位累加器N=23bit,則:

(2)掃頻信號部分DDS 由于FPGA片內資源豐富,為保證足夠的掃頻精度,取參考時鐘頻率fclk為40 MHz。通過控制頻率控制字K的變化范圍,完全可以滿足DAC0800的速度要求。

3.2 相位測量相關計算

由FPGA利用等精度法測得被測信號和基準時鐘的頻率分別為f0、fCP,對被測信號鑒相后,由得到的相位差脈沖寬度T控制計數器計數,其計數值設為M,則被測信號的相位差為:

(1)相位測量誤差計算 若讓計數器在1 s內累計記數,則累計數:M1=Mf0,式(5)改為

![]()

其測量誤差△φ為:

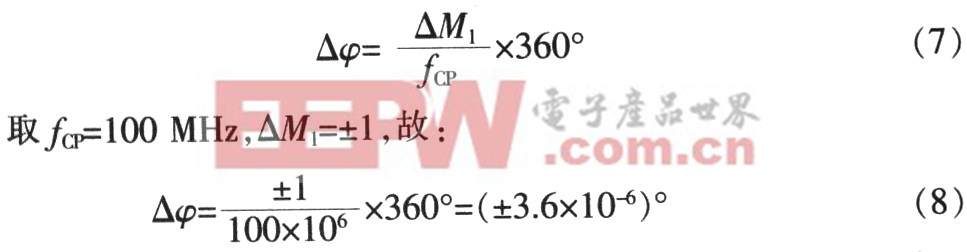

(2)相位測量分辨率計算 數字移相信號發生器頻率范圍為20 Hz~20 kHz,相位差測量范圍為0~359°,因此計數器時鐘頻率fclk至少為72 MHz,取fCP=100 MHz,由于計數器分辨率為±1,對應最小相位分辨率(f0=20 kHz時):

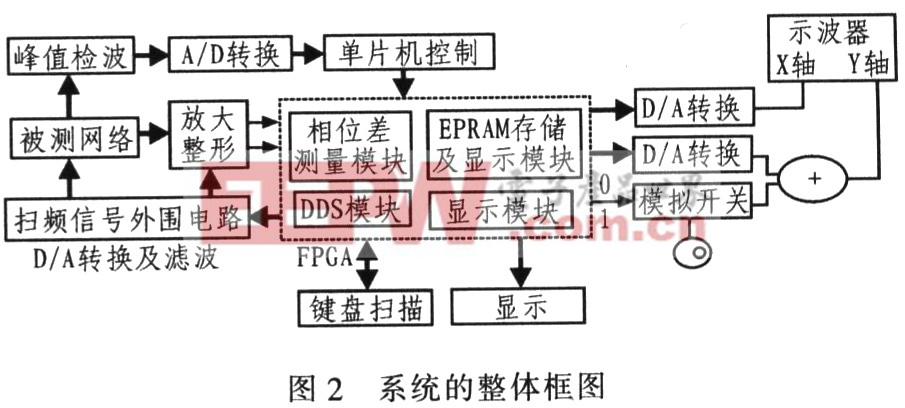

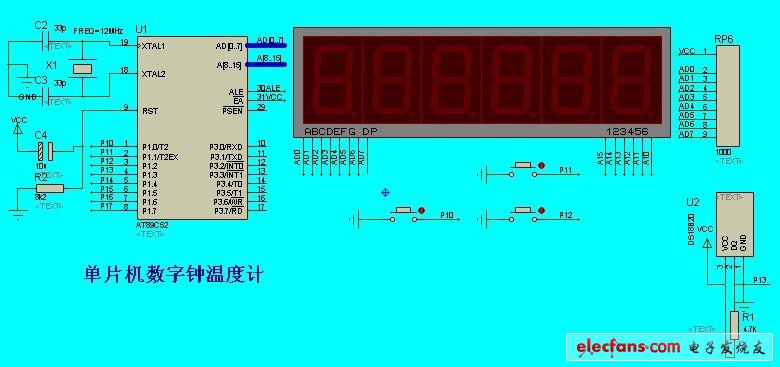

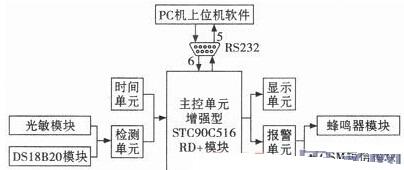

4 系統整體框圖

系統設計發揮FPGA穩定、可靠、可編程的特點,讓FP-GA實現盡可能多的功能,從而減少模擬部分的工作,使整個設計更加可靠。系統整體框圖如圖2所示。

評論