S3C2410外圍存儲(chǔ)系統(tǒng)的研究與設(shè)計(jì)

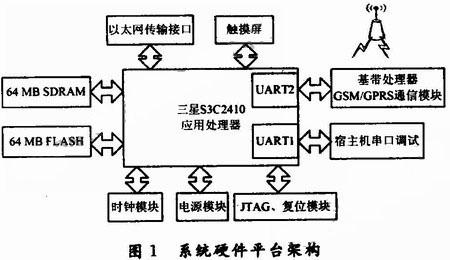

Samsung公司推出的基于ARM920T內(nèi)核的16/32位RISC微處理器S3C2410,為手持設(shè)備和一般類型應(yīng)用提供了低價(jià)格、低功耗、高性能小型微控制器的解決方案。為了降低整個(gè)系統(tǒng)的成本,S3C2410提供了豐富的內(nèi)部設(shè)備。其中加強(qiáng)的ARM體系結(jié)構(gòu)MMU用于支持WinCE,EPOC32和Linux。隨著技術(shù)的進(jìn)步和發(fā)展,電子產(chǎn)品的功能日益強(qiáng)大,而嵌入式操作系統(tǒng)可以有效地管理各項(xiàng)功能,并且能夠縮短產(chǎn)品開發(fā)周期,因此將微處理器與嵌入式操作系統(tǒng)進(jìn)行聯(lián)合開發(fā)成為一種趨勢(shì),然而微處理器的片內(nèi)存儲(chǔ)資源有限,若要進(jìn)行嵌入式系統(tǒng)的移植,必須擴(kuò)展其存儲(chǔ)系統(tǒng)。對(duì)于嵌入式系統(tǒng)的開發(fā)人員來(lái)說(shuō),深入理解其存儲(chǔ)系統(tǒng)原理和有效地管理存儲(chǔ)系統(tǒng)對(duì)正確高效地設(shè)計(jì)嵌入式系統(tǒng)的硬件和底層軟件編程具有重要的意義[1]。

1 S3C2410的尋址原理

ARM920T內(nèi)核提供了32位的地址總線,可以訪問4G(232)的線性地址空間,而S3C2410的內(nèi)部地址總線是30bit(HADDR[29:0]),能夠訪問的最大外部地址空間是230,即1G的地址空間0x00000000~0x3FFFFFFFF,可見S3C2410僅利用了ARM920T的32位地址總線的低30位,并且是一一對(duì)應(yīng)相連的[1]。由表1可知S3C2410將1G的外部地址空間分成了8?jìng)€(gè)存儲(chǔ)器組,每個(gè)組的大小為128M,其中6個(gè)用于ROM、SRAM等存儲(chǔ)器,2個(gè)用于ROM、SRAM、SDRAM等存儲(chǔ)器。基于芯片體積及成本的考慮,當(dāng)S3C2410對(duì)外尋址時(shí),采用了部分譯碼的方式,即低位地址線用于外圍存儲(chǔ)器的片內(nèi)尋址,而高位地址線用于外圍存儲(chǔ)器的片外尋址。如表1所示,由于每個(gè)存儲(chǔ)器組的起始地址及空間大小固定,對(duì)于系統(tǒng)要訪問的任意外部地址,S3C2410可以方便地利用內(nèi)部地址總線的高3位HADDR[29:27]來(lái)選擇該地址屬于哪一個(gè)存儲(chǔ)器組(Bank),從而激活相應(yīng)的Bank選擇信號(hào),并且使用外部地址總線A[26:0]來(lái)實(shí)現(xiàn)相應(yīng)Bank的內(nèi)部尋址,尋址范圍為128M(227),從而使得其外圍地址訪問空間為1GB(128MB×8)。S3C2410正是通過這種機(jī)制來(lái)完成外部地址空間的尋址全過程。

S3C2410訪問SDRAM地址空間的過程比較難理解,這主要和SDRAM的存儲(chǔ)結(jié)構(gòu)有關(guān)。為了更深入地理解其尋址機(jī)制,筆者以SDRAM芯片HY57V561620B(32MB)為例進(jìn)行詳細(xì)地說(shuō)明。該芯片的內(nèi)部存儲(chǔ)結(jié)構(gòu)是4Banks×4M×16Bit,即共有4個(gè)Bank,每個(gè)Bank中有4M個(gè)半字(16Bit)。Bank地址可以通過BA[1:0]與地址總線的高位相連來(lái)確定,具體BA[1:0]與哪個(gè)地址位相連,不同的SDRAM存儲(chǔ)系統(tǒng)有不同的方案,詳見參考文獻(xiàn)[3]。而每個(gè)Bank中的存儲(chǔ)單元由行地址和列地址來(lái)唯一標(biāo)識(shí)[1],該芯片通過行地址鎖存引腳nRAS和列地址鎖存引腳nCAS分別與S3C2410的引腳nSRAS(SDRAM行地址選通信號(hào))和nSCAS(SDRAM列地址選通信號(hào))連接,從地址總線獲得行地址和列地址。而且列地址的位數(shù)可以在BANKCONn(n=6,7)的中的SCAN——BANKCONn [1:0]來(lái)配置,00=8-bit,01=9-bit,10=10-bit,其復(fù)位值為00,即8bit。

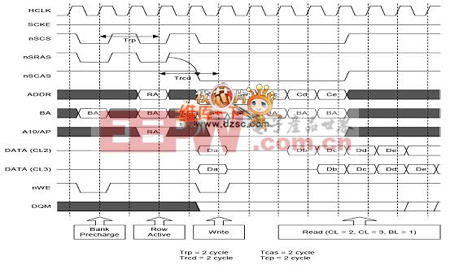

在實(shí)際工作中,如圖1所示,在第3個(gè)總線時(shí)鐘,nSCS為低電平,表示SDRAM被選中,并且地址線的Bank地址與相應(yīng)的行地址同時(shí)發(fā)出,這個(gè)命令稱之為“行有效”或“行激活”(Row Active)。此時(shí)SDRAM將行地址鎖存(nSRAS有效),但還沒有執(zhí)行寫命令(nWE為高電平),因?yàn)闆]有列地址(nSCAS為高電平),存儲(chǔ)單元無(wú)法確定。經(jīng)過Trcd(RAS至CAS延遲)后,SDRAM再次被選中(nSCS為低電平),此時(shí)nSCAS為低電平,指示SDRAM此時(shí)地址線上的地址為列地址,同時(shí)nWE有效,寫操作被執(zhí)行。可見發(fā)送列地址尋址命令與具體的操作命令(是讀還是寫),這兩個(gè)命令也是同時(shí)發(fā)出的,所以一般都會(huì)以“讀/寫命令”來(lái)表示列尋址,相關(guān)的列地址被選中之后,將會(huì)觸發(fā)數(shù)據(jù)傳輸。至此,S3C2410對(duì)SDRAM的尋址就完成了。可見,S3C2410將地址總線上的地址分成行地址和列地址并分開傳輸給SDRAM。基于上述的尋址機(jī)制,由BA[1:0]和12根地址線就可以尋址32M或更大的地址空間了。

圖 1 S3C2410 SDRAM時(shí)序圖

2 存儲(chǔ)器控制器和相關(guān)引腳介紹

2.1寄存器介紹

S3C2410存儲(chǔ)器控制器主要有:總線帶寬和等待控制寄存器(BWSCON);總線控制寄存器(BANKCONN:nGCS0-nGCS5);BANK控制寄存器(BANKCONn:nGCS6-nGCS7);刷新控制寄存器(REFRESH);BANKSIZE寄存器;SDRAM模式寄存器集寄存器(MRSR)等,詳情請(qǐng)見參考文獻(xiàn)[3]。

2.2相關(guān)引腳

S3C2410提供了相關(guān)的引腳來(lái)控制存儲(chǔ)器訪問:

組選擇信號(hào):nGCS0-nGCS5,nGCS6(nSCS0),nGCS7(nSCS1)引腳用來(lái)選擇相應(yīng)的存儲(chǔ)器組。

訪問控制信號(hào):為了實(shí)現(xiàn)ARM存儲(chǔ)器訪問指令LDR/STR字節(jié)、半字和字訪問的三種方式,在S3C2410的存儲(chǔ)器組中,除了Bank0以外的所有地址空間都可以通過編程設(shè)置為8位、16位或32位對(duì)準(zhǔn)訪問,Bank0可以設(shè)置為16位或32位。引腳nWBE[3:0](寫字節(jié)使能)實(shí)現(xiàn)8bit ROM芯片組的三種訪問方式,或者SRAM不使用UB/LB(在BWSCON中設(shè)置)的情況下,與UB/LB連接。引腳nBE[3:0](在使用SRAM情況下的字節(jié)允許信號(hào))在SRAM使用UB/LB(是否使用可在BWSCON中設(shè)置)的情況下與UB/LB連接。DQM[3:0](SDRAM數(shù)據(jù)屏蔽信號(hào))引腳實(shí)現(xiàn)對(duì)SDRAM的三種訪問。還有nWAIT、nXBREQ/nXBACK引腳。

存儲(chǔ)器相關(guān)文章:存儲(chǔ)器原理

評(píng)論