基于MAX II系列CPLD 的LCD控制器設(shè)計(jì)

0前言

液晶顯示屏(LCD)是薄型平面顯示設(shè)備,由排列在光源或者反射器之前一定數(shù)量的彩色或者單色象素構(gòu)成。這類顯示屏已經(jīng)成為大部分嵌入式系統(tǒng)不可缺少的組成部分。但是在嵌入式系統(tǒng)中八位和十六位微處理器大多沒(méi)有內(nèi)置的LCD控制器,又由于LCD屏的分辨率很高,即使有內(nèi)置的LCD控制器,也較難進(jìn)行控制;另外內(nèi)置LCD控制器對(duì)內(nèi)存帶寬的占用較高,使控制器所能支配的資源也會(huì)變得非常有限。因此在微處理器和LCD屏之間加上一個(gè)LCD控制器是非常必要的。常用的LCD控制器主要有兩種:專用的控制芯片和基于可編程器件的控制器。本文采用Altera公司的MAX II系列CPLD器件來(lái)實(shí)現(xiàn)LCD控制器。CPLD一般使用外加的串行EEPROM來(lái)存儲(chǔ)非易失信息,而MAX II CPLD是唯一具有用戶閃存(UFM)的CPLD,它支持用戶存儲(chǔ)高達(dá)8Kbits的非易失信息,因此不需要采用外部存儲(chǔ)器,并且在實(shí)現(xiàn)LCD控制器時(shí)還可以利用CPLD的內(nèi)部UFM振蕩器來(lái)滿足時(shí)鐘需求,從而避免了采用外部時(shí)鐘信號(hào)。這些獨(dú)特的功能使MAX II CPLD成為實(shí)現(xiàn)LCD控制器最好的目標(biāo)器件。

1 嵌入式系統(tǒng)的LCD接口電路結(jié)構(gòu)

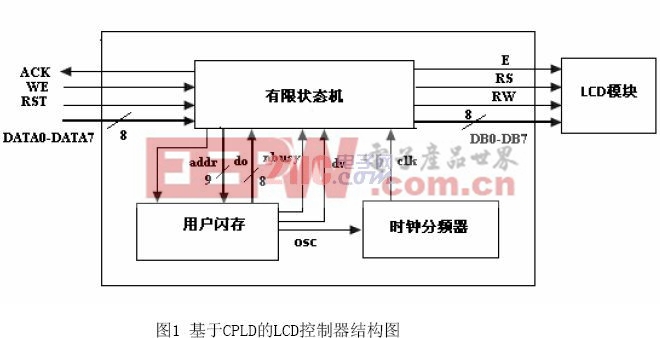

基于MAX II CPLD的LCD接口電路一般采用圖1所示結(jié)構(gòu)。圖中LCD接口電路負(fù)責(zé)接受微處理器的配置,通過(guò)總線把DRAM上保存的顯示數(shù)據(jù)讀出,然后按照屏類型和顯示設(shè)置轉(zhuǎn)換為需要的格式,并按照屏?xí)r序要求發(fā)送出去。在設(shè)計(jì)顯示控制器時(shí),需要注意如下幾個(gè)方面:支持的屏類型、總線類型的選擇、同微處理器之間的交互方式、動(dòng)態(tài)圖像顯示和中斷設(shè)計(jì)。基于CPLD的LCD控制器可以提供合適的顯示單元,它產(chǎn)生需要的時(shí)序信號(hào),滿足LCD的時(shí)序要求,同時(shí)卸載了微處理器和控制器繁重的LCD處理任務(wù),從而提高了處理器和控制器執(zhí)行其他操作的效率。

2 LCD 控制器組成與接口信號(hào)

2.1 LCD 控制器組成

由圖1可知,LCD控制器有三個(gè)主要模塊:有限狀態(tài)機(jī)(FSM)、時(shí)鐘分頻器和用戶閃存(UFM)模塊。

1、初始化LCD和有限狀態(tài)機(jī)模塊

FSM模塊有8個(gè)不同的狀態(tài)。它用于初始化LCD,初始化完成后顯LCD進(jìn)行讀寫操作。圖2所示為L(zhǎng)CD模塊的初始化步驟。為簡(jiǎn)化初始化過(guò)程,每次發(fā)送一條命令后,延時(shí)15ms(而不是檢查忙標(biāo)志的狀態(tài))。但是向LCD模塊寫入數(shù)據(jù)時(shí),每一數(shù)據(jù)寫操作之后,要檢查忙標(biāo)志的狀態(tài)。這樣就加速了寫操作過(guò)程。

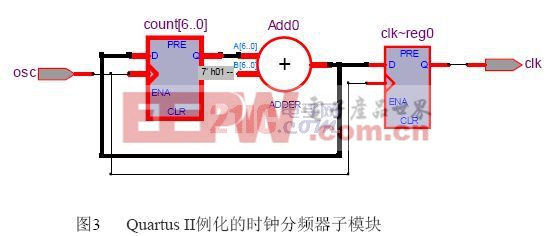

2、時(shí)鐘分頻器模塊

時(shí)鐘分頻器模塊主要是降低內(nèi)部振蕩器輸出頻率,從而滿足了LCD模塊的時(shí)序要求以及控制器的性能要求。該模塊把振蕩器輸出信號(hào)osc的頻率由.5MHz降低到43kHz左右。降低頻率以后的信號(hào)(即Clk信號(hào))從時(shí)鐘分頻器模塊輸出(見(jiàn)圖3)。該模塊主要代碼為:

module divider (osc, clk);

input osc;

output clk;

reg clk;

reg [6:0]count;

initial

begin

count = 7'b0000000;

end

always @ (posedge(osc))

begin

count = count + 7'b0000001;

clk = count[6];

end

endmodule

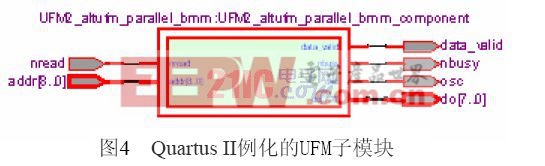

3、用戶閃存模塊

MAX II CPLD中的用戶閃存UFM模塊主要用于存儲(chǔ)LCD控制器打開(kāi)之后,需要在LCD屏上顯示的信息。采用十六進(jìn)制(Intel格式)文件(.hex)對(duì)UFM進(jìn)行設(shè)置,并利用UFM宏功能進(jìn)行例化。

UFM模塊接口信號(hào)主要有addr、nread、do、dv、osc和clk信號(hào):

Addr為9位地址總線,用于選擇UFM的某一存儲(chǔ)位置。

nread 若該信號(hào)設(shè)置為0,以讀取地址總線所指向存儲(chǔ)器的內(nèi)容。

do 為數(shù)據(jù)輸出信號(hào)。8位數(shù)據(jù)總線,保持地址總線所指向16位存儲(chǔ)器的高8位。

dv 為數(shù)據(jù)有效信號(hào)。該信號(hào)指示8位數(shù)據(jù)總線上的數(shù)據(jù)有效并且可讀。

osc 為UFM模塊內(nèi)部振蕩器輸出。輸出信號(hào)到時(shí)鐘分頻器,輸出頻率為5.5MHz。

2.2 LCD 控制器接口信號(hào)

1、LCD控制器與LCD屏之間的接口信號(hào)

LCD控制器與LCD模塊之間的接口信號(hào)有E、RS、RW 、DB0-DB7:

E為使能選通信號(hào)。該信號(hào)下降沿將雙向總線上的數(shù)據(jù)鎖存到數(shù)據(jù)或者命令寄存器中,反之亦然。

RS為寄存器選擇信號(hào)。用于選擇LCD模塊的數(shù)據(jù)和命令寄存器。當(dāng)RS=0時(shí)為命令寄存器;

RS=1時(shí)為數(shù)據(jù)寄存器。

RW為區(qū)分讀寫操作的讀寫信號(hào)。RW=0:寫操作;RW=1:讀操作

DB0-DB7為8位雙向總線,承載LCD模塊的數(shù)據(jù)和命令。

2、LCD控制器與微處理器之間的接口信號(hào)

LCD控制器與微處理器之間的接口信號(hào)有DATA0-DATA7、RST、WE、ACK:

DATA0-DATA7 為處理器和控制器的8位總線,承載LCD模塊上顯示的ASCII字符值。

RST 為復(fù)位信號(hào)。該信號(hào)用于復(fù)位控制器,再次初始化LCD模塊。

WE 為寫使能信號(hào)。該信號(hào)指示寫周期的開(kāi)始。應(yīng)將它設(shè)為低電平,使能對(duì)LCD模塊的寫操作。

ACK 為應(yīng)答信號(hào)。該信號(hào)指示數(shù)據(jù)已經(jīng)成功地發(fā)送到LCD模塊,準(zhǔn)備接收后面的數(shù)據(jù)。

在此信號(hào)變?yōu)榈碗娖街鞍l(fā)送的任何數(shù)據(jù)都被控制器忽略。

3設(shè)計(jì)與仿真

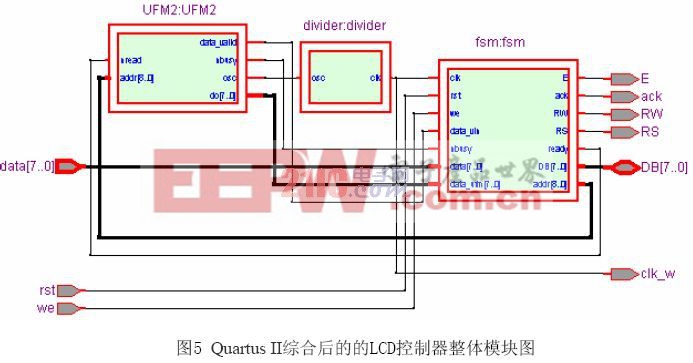

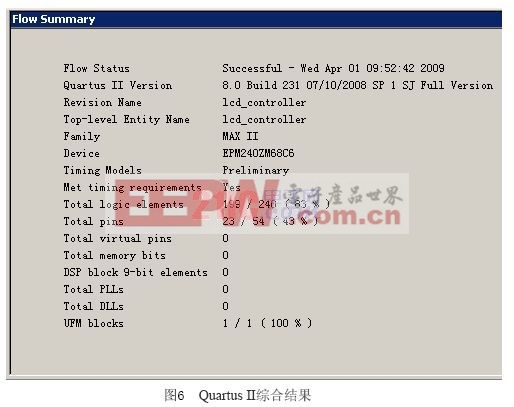

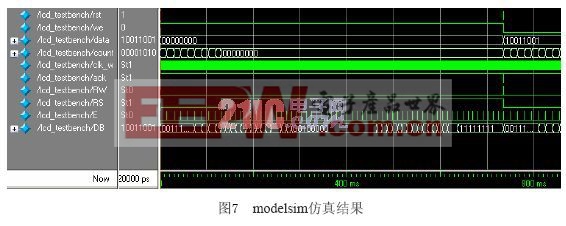

本設(shè)計(jì)通過(guò)MAX II CPLD EPM240ZM成功地實(shí)現(xiàn)了處理器和LCD模塊的接口,圖5-圖7分別給出了LCD控制器的整體模塊、綜合結(jié)果和仿真波形。

4結(jié)論

本設(shè)計(jì)采用MAX II系列CPLD器件EPM240ZM來(lái)實(shí)現(xiàn)LCD控制器,解決了微處理器與LCD顯示模塊之間的接口問(wèn)題,并在OptrexSC1602D 16×2字符LCD模塊上實(shí)現(xiàn)了嵌入式系統(tǒng)的顯示功能。由于是使用一片MAX II CPLD芯片完成LCD全部的時(shí)序控制、顯示控制等功能,所以是接口電路變得更加簡(jiǎn)潔、可靠,具有很好的應(yīng)用價(jià)值。

本文作者創(chuàng)新點(diǎn): 使用唯一具有用戶閃存(UFM)的MAX II CPLD,不需要采用外部存儲(chǔ)器就實(shí)現(xiàn)了LCD 全部的時(shí)序控制、顯示控制等功能,使LCD 接口電路變得更加簡(jiǎn)潔、可靠。

評(píng)論